EDA技术是现代集成电路和电子系统设计的基石,它贯穿了从概念构思到产品量产的整个生命周期,EDA就是利用计算机软件和硬件,帮助电子工程师设计、验证、制造和测试电子产品的技术。

下面,我将按照电子产品设计的典型流程,分阶段详细介绍EDA技术的具体应用。

芯片设计领域

这是EDA技术最核心、最复杂的应用领域,尤其对于超大规模集成电路的设计至关重要。

设计与仿真

这是芯片设计的起点,工程师在软件中创建和验证电路的功能。

-

应用描述:

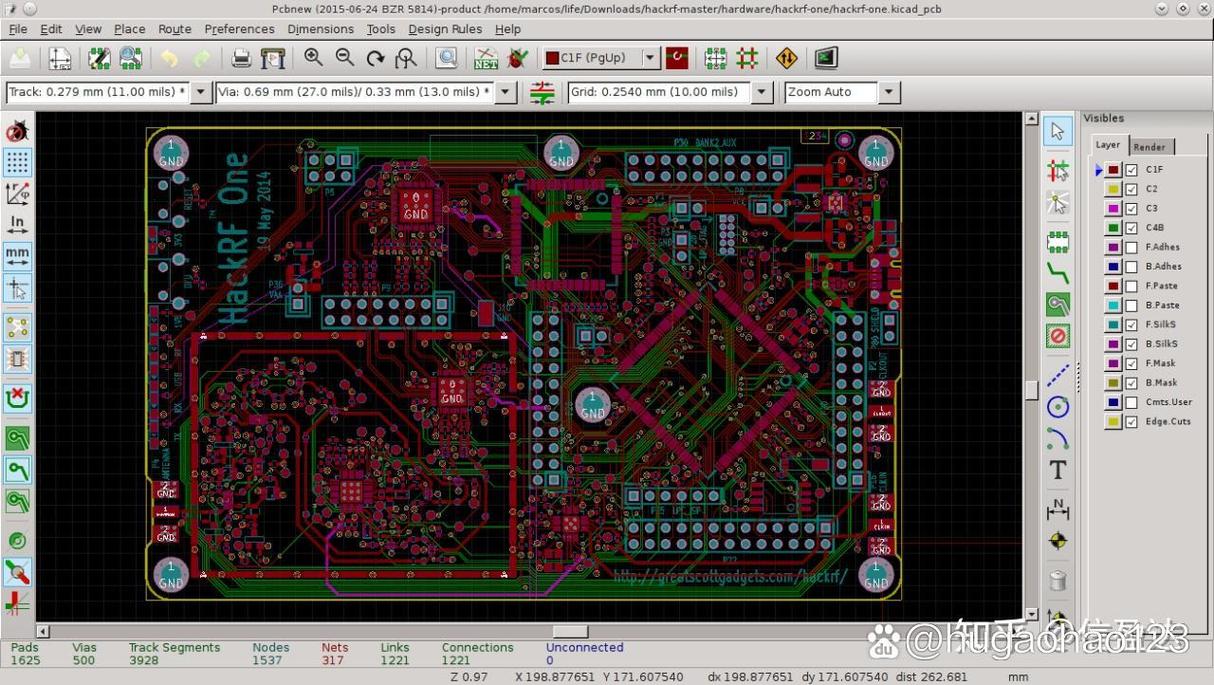

(图片来源网络,侵删)

(图片来源网络,侵删)- 原理图设计: 工程师使用EDA工具(如Cadence OrCAD Capture, Altium Designer)绘制电路的原理图,定义各个元器件(电阻、电容、逻辑门等)及其连接关系,这就像在纸上画电路图,但软件可以自动进行电气规则检查。

- 硬件描述语言 编写与仿真: 对于数字芯片,工程师使用Verilog或VHDL等语言来描述电路的行为和结构,EDA仿真工具(如Synopsys VCS, Cadence Xcelium)可以对这些代码进行功能仿真,验证其逻辑是否正确,而无需等待物理芯片制造出来,这极大地加快了设计迭代速度。

-

常用工具: Cadence OrCAD, Altium Designer, Synopsys VCS, Cadence Xcelium, ModelSim/QuestaSim。

逻辑综合与布局布线

这是将抽象设计转化为物理布局的关键步骤。

-

应用描述:

- 逻辑综合: 工程师将RTL代码(用Verilog/VHDL描述的行为级设计)输入到综合工具(如Synopsys Design Compiler)中,工具会根据指定的工艺库,自动将代码转换为由标准逻辑单元(与门、或门、触发器等)组成的门级网表。

- 布局布线: 这是芯片物理设计的核心。

- 布局: 工具(如Synopsys IC Compiler, Cadence Innovus)会自动决定数百万甚至数十亿个晶体管在芯片硅片上的最佳位置,目标是优化性能、功耗和面积。

- 布线: 在确定好单元位置后,工具会自动在它们之间连接金属连线,形成最终的电路通路,这个过程极其复杂,需要考虑信号完整性、功耗、时序等无数约束。

-

常用工具: Synopsys Design Compiler (综合), Synopsys IC Compiler / Cadence Innovus (布局布线)。

验证与测试

确保芯片功能正确、性能达标且无制造缺陷。

-

应用描述:

- 静态时序分析: 在布局布线后,STA工具(如Synopsys PrimeTime)会分析电路在不同工艺、电压、温度下的延迟,确保所有信号都能在规定的时间内正确到达,满足时序要求,这是验证芯片能否正常工作的关键一步。

- 形式验证: 用于比较不同设计版本(如综合前后的网表)在逻辑上是否等价,确保设计转换过程中没有引入错误。

- 物理验证: 包括设计规则检查 和版图原理图对比,DRC确保芯片的物理布局符合制造厂的工艺规则(如线宽、间距),LVS确保最终画出的物理版图与逻辑设计的网表完全一致。

- 可测性设计: 在设计阶段就插入测试逻辑(如扫描链),使得制造出来的芯片可以方便地进行自动化测试,快速找出制造缺陷。

-

常用工具: Synopsys PrimeTime (STA), Mentor Calibre (DRC/LVS), Synopsys VCS (验证)。

模拟/混合信号设计

对于包含模拟电路(如放大器、滤波器、ADC/DAC)的芯片,EDA应用有所不同。

-

应用描述:

- 电路仿真: 使用SPICE(Simulation Program with Integrated Circuit Emphasis)及其商业版本(如Cadence Virtuoso Spectre, Synopsys HSPICE)对模拟电路进行精确的仿真,分析其直流、交流、瞬态等特性。

- 版图设计: 模拟电路的版图通常需要工程师手动或半手动绘制,对匹配、对称性、噪声隔离等有极高的要求,EDA工具(如Cadence Virtuoso)提供强大的版图编辑和仿真环境。

-

常用工具: Cadence Virtuoso, Synopsys HSPICE, Cadence Spectre。

印刷电路板 设计领域

对于绝大多数电子产品(如手机、电脑、家电),EDA技术也广泛应用于PCB的设计。

原理图设计

与芯片设计类似,工程师使用EDA工具绘制整个电子系统的电路连接图。

-

应用描述: 定义系统中的各个元器件(如微控制器、内存、传感器)及其电气连接关系,并进行初步的电气规则检查。

-

常用工具: Altium Designer, Cadence Allegro, KiCad, Eagle。

PCB布局布线

将原理图转化为可以实际制造的PCB物理板。

-

应用描述:

- 布局: 工程师或工具自动将元器件合理地放置在PCB板上,考虑的因素包括:信号完整性、散热、机械结构、可制造性等。

- 布线: 在元器件之间绘制铜箔走线,连接电气节点,对于高速PCB(如DDR、PCIe),需要严格控制走线的长度、阻抗匹配、串扰等。

-

常用工具: Altium Designer, Cadence Allegro, Zuken CR-8000。

高级分析与验证

确保PCB在高速、高频环境下能稳定工作。

-

应用描述:

- 信号完整性 分析: 仿真信号在走线上的传输,分析是否存在反射、串扰、振铃等问题,确保数据传输无误。

- 电源完整性 分析: 仿真电源和地网络的分布,分析电压波动和地弹,保证芯片获得稳定纯净的供电。

- 电磁兼容性 分析: 预测PCB工作时产生的电磁辐射,以及对外部电磁干扰的敏感度,确保产品通过EMC认证。

-

常用工具: Cadence Sigrity, Mentor HyperLynx, Ansys SIwave。

系统级与封装领域

随着系统级封装 和2.5D/3D封装技术的发展,EDA的应用也扩展到了更宏观的层面。

系统级封装设计

- 应用描述: 将多个裸片、无源元件等封装在一个封装体内,实现更高性能和更小尺寸,EDA工具(如Cadence Virtuoso System Design)用于进行多芯片、多物理域(电、热、机械)的协同设计和仿真,确保整个SiP系统的性能和可靠性。

先进封装设计

- 应用描述: 对于2.5D(如CoWoS)和3D封装,EDA工具用于设计复杂的硅中介层、硅通孔,并分析多芯片堆叠带来的热管理、信号完整性等挑战。

半导体制造领域

EDA技术不仅用于设计,也深度参与制造环节。

光罩数据生成

- 应用描述: 芯片最终的设计版图需要转换为一套被称为“光罩”的玻璃模板,EDA工具(如Synopsys IC Validator)会根据物理验证通过的版图数据,生成用于光刻机的光罩数据文件。

计量与良率提升

- 应用描述: 在制造过程中,EDA工具可以分析从生产线上收集的大量数据,找出导致芯片缺陷或性能偏差的设计原因,从而指导设计优化,提高制造良率。

总结表格

| 设计阶段 | 主要任务 | EDA技术/工具示例 |

|---|---|---|

| 芯片设计 | ||

| 功能设计 | 原理图绘制、HDL代码编写与仿真 | Cadence OrCAD, Synopsys VCS, ModelSim |

| 物理设计 | 逻辑综合、布局布线 | Synopsys Design Compiler, Cadence Innovus |

| 验证测试 | 时序分析、形式验证、物理验证 | Synopsys PrimeTime, Mentor Calibre |

| 模拟设计 | 电路仿真、版图绘制 | Cadence Virtuoso, Synopsys HSPICE |

| PCB设计 | ||

| 系统设计 | 原理图设计 | Altium Designer, Cadence Allegro |

| 物理实现 | PCB布局布线 | Altium Designer, Cadence Allegro |

| 高级分析 | 信号/电源完整性分析 | Cadence Sigrity, Mentor HyperLynx |

| 系统与封装 | ||

| SiP/先进封装 | 多芯片协同设计、热/电/力仿真 | Cadence Virtuoso System Design, Ansys |

| 半导体制造 | ||

| 生产准备 | 光罩数据生成 | Synopsys IC Validator |

| 良率提升 | 数据分析、工艺控制 | 各种数据分析平台 |

EDA技术是现代电子产业的“空气和水”,它无处不在,没有EDA,就没有今天高性能的CPU、GPU,也没有功能强大的智能手机和复杂的通信设备,它将工程师从繁重的手工劳动中解放出来,使得设计数十亿晶体管的复杂芯片成为可能。