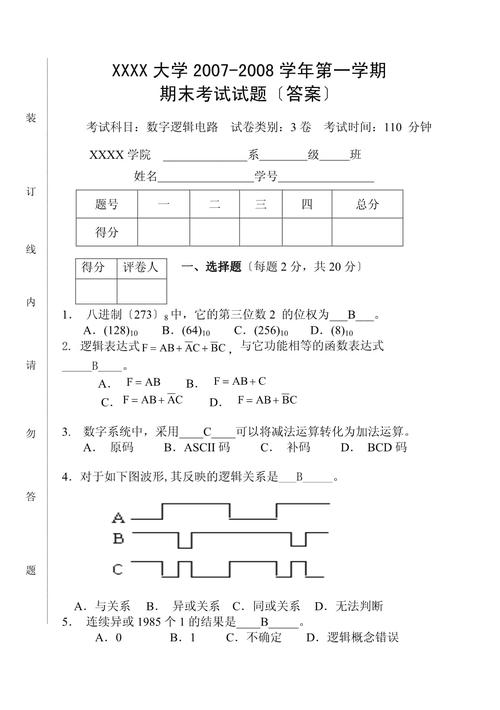

《数字电子技术》课程期末试卷(A卷)

考试时间: 120分钟 总分: 100分 班级: ____ 学号: ____ 姓名: ____

填空题(每空1分,共20分)

- 数字电路中,最基本的逻辑关系有与、__、__三种。

- (10110.101)₂ = ( __ )₁₀ = ( __ )₁₆。

- 逻辑函数的表示方法主要有真值表、__、__和卡诺图四种。

- TTL门电路中,输出为低电平时的状态称为__态,此时输出管处于__工作状态。

- 一个触发器可以存储__位二进制信息,要构成一个N位寄存器,需要__个触发器。

- 描述时序逻辑电路功能的方程组通常包括:输出方程、__方程和__方程。

- 同步计数器是指计数脉冲同时加到__上,各触发器的状态翻转由__决定。

- 单稳态触发器有一个__态和一个__态,其输出脉冲的宽度由__电路的参数决定。

- 在数模转换器中,分辨率是指DAC能够分辨出的__电压变化量,其值与输入数字量的__有关。

- 存储器按工作方式可分为随机存取存储器(RAM)和__,RAM根据存储原理可分为静态RAM(SRAM)和__。

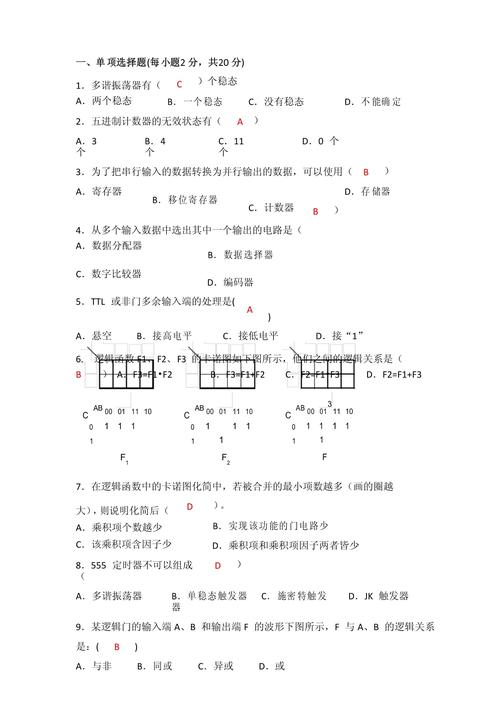

选择题(请将正确答案的字母填入括号内,每题2分,共20分)

-

下列逻辑代数公式中,错误的是。 A. A + A = A B. A + AB = A C. A + ĀB = A + B D. AB + AC + BC = AB + AC

-

将十进制数25转换为8421BCD码,其结果为。 A. 10101 B. 00100101 C. 11001 D. 100101

-

下列逻辑门中,可以实现“线与”功能的是。 A. 与非门 B. 或非门 C. OC门(集电极开路门) D. 三态门

-

一个4选1的数据选择器,其地址输入端应有。 A. 1个 B. 2个 C. 3个 D. 4个

(图片来源网络,侵删)

(图片来源网络,侵删) -

JK触发器的特征方程为Qⁿ⁺¹ = JQⁿ + KQⁿ,要使其构成T'触发器(即每来一个时钟脉冲就翻转一次),正确的接法是。 A. J=K=0 B. J=K=1 C. J=1, K=0 D. J=0, K=1

-

欲设计一个能存放4位二进制代码的寄存器,需要使用个触发器。 A. 2 B. 4 C. 8 D. 16

-

一个8位D/A转换器,其参考电压VREF=5V,当输入数字量为10000000时,其输出电压为。 A. 2.5V B. 5V C. 0V D. 1.25V

-

下列电路中,属于组合逻辑电路的是。 A. 计数器 B. 移位寄存器 C. 编码器 D. 节拍脉冲发生器

(图片来源网络,侵删)

(图片来源网络,侵删) -

对于CMOS门电路,其静态功耗。 A. 较大 B. 较小 C. 为零 D. 不确定

-

一个具有N个地址输入端和M个数据输出端的ROM,其存储容量为。 A. N × M B. 2^N × M C. N + M D. 2^(N+M)

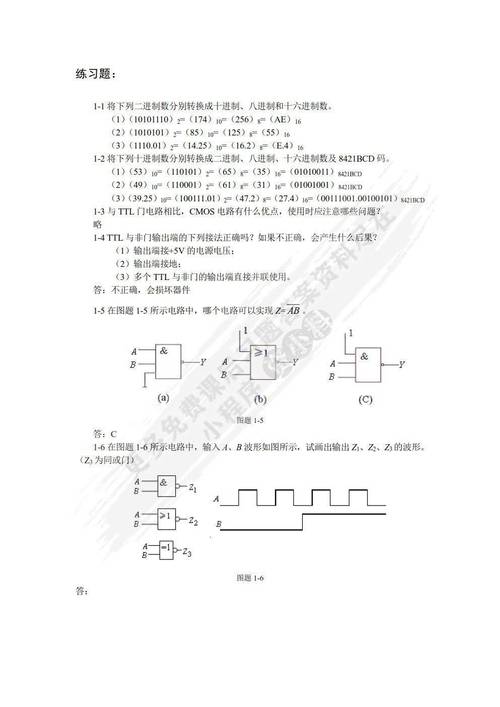

分析与化简题(共20分)

-

(10分)用卡诺图法化简逻辑函数 Y(A,B,C,D) = Σm(0, 2, 5, 7, 8, 10, 13, 15),并写出最简“与或”表达式。

-

(10分)分析下图所示组合逻辑电路的功能,写出输出F的逻辑表达式,并判断其实现的是什么功能。

(此处应有一个逻辑电路图,由两个与非门和一个或门构成,输入为A, B, C, D) 假设电路图如下:

A ----| | | NAND|---- F B ----|_____| | | OR | C ----| |----| | NAND| D ----|_____|(请根据实际试卷中的电路图进行分析)

设计题(共20分)

-

(10分)试用3线-8线译码器74LS138和必要的逻辑门设计一个多输出逻辑电路,其输出逻辑函数为: Y₁ = ABC + ABC Y₂ = ABC + ABC + ABC Y₃ = ABC (要求:写出设计思路,画出逻辑电路图。)

-

(10分)试用下降沿触发的JK触发器设计一个同步三进制加法计数器,要求:

- 列出状态转换表。

- 求出每个触发器的驱动方程(J, K表达式)。

- 画出逻辑电路图。

综合应用题(共20分)

-

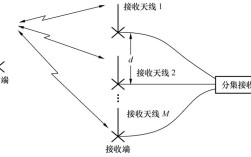

(12分)分析下图所示时序逻辑电路。

- (1)判断该电路是同步时序电路还是异步时序电路?

- (2)写出电路的驱动方程、状态方程和输出方程。

- (3)列出状态转换表,画出状态转换图。

- (4)说明该电路的逻辑功能。

(此处应有一个时序逻辑电路图,由两个JK触发器构成,CLK信号同时连接到两个触发器的时钟输入端) 假设电路图如下:

CP (CLK) ----|>----[JK-FF1]---- Q1 ---- | | | | |---------| | | | | J | K | Y (Output) X ----|>----[JK-FF2]---- Q2 ----| | | | | |---------| | J | K | Q2 ----------------------------|(请根据实际试卷中的电路图进行分析)

-

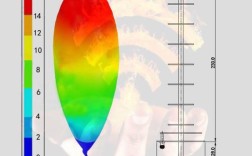

(8分)555定时器接成下图所示电路。

- (1)指出该电路的名称,并简述其工作原理。

- (2)已知R₁=10kΩ,R₂=20kΩ,C=0.01μF,VCC=5V,计算输出脉冲的周期T和高电平时间T_H。

(此处应有一个555定时器构成的电路图,多谐振荡器电路) 假设电路图如下:

VCC | R1 | +----+-----> 输出 (OUT) | | R2 C | | +----+-----> 地 (GND) | DIS (7脚)(请根据实际试卷中的电路图进行分析)

参考答案(要点)

填空题

- 或,非

- 625, 16.A

- 逻辑表达式,逻辑图

- 开关,饱和

- 1,N

- 驱动,状态

- 所有触发器,时钟脉冲CP

- 稳定,暂稳,RC

- 最小,位数

- 只读存储器,动态RAM

选择题

- D

- B

- C

- B

- B

- B

- A

- C

- B 10