《数字电子技术基础》核心知识点总结

第一章 数字逻辑基础

-

数字信号与数字电路

(图片来源网络,侵删)

(图片来源网络,侵删)- 数字信号:在时间上和幅值上都是离散的信号,通常用高电平(逻辑1)和低电平(逻辑0)表示。

- 数字电路:用于处理数字信号的电子电路,具有抗干扰能力强、可靠性高、便于集成等优点。

-

数制与码制

- 常用数制:

- 二进制:基数为2,数码为0, 1,计算机内部处理的基础。

- 八进制:基数为8,数码为0, 1, 2, ..., 7。

- 十六进制:基数为16,数码为0, 1, ..., 9, A, B, C, D, E, F。

- 数制转换:

- 非十进制 → 十进制:按权展开求和。

- 十进制 → 非十进制:整数部分“除基取余”,小数部分“乘基取整”。

- 二进制 ↔ 八/十六进制:分组转换(3位一组对应八进制,4位一组对应十六进制)。

- 码制:

- BCD码 (Binary-Coded Decimal):用4位二进制数表示一位十进制数。

- 8421码:最常用,4位权值分别为8, 4, 2, 1。

- 5421码、2421码:有权码。

- 余3码:无权码,由8421码加3(0011)得到,具有自补特性。

- 格雷码:相邻两个代码之间只有一位不同,常用于消除竞争冒险。

- ASCII码:美国信息交换标准代码,用于字符编码。

- BCD码 (Binary-Coded Decimal):用4位二进制数表示一位十进制数。

- 常用数制:

-

逻辑代数基础

- 基本逻辑运算:

- 与逻辑:

Y = A · B(或Y = AB),所有条件都满足时,结果才成立。 - 或逻辑:

Y = A + B,任一条件满足时,结果就成立。 - 非逻辑:

Y = A'或Y = ¬A,结果与条件相反。

- 与逻辑:

- 复合逻辑运算:

- 与非:

Y = (A · B)' - 或非:

Y = (A + B)' - 与或非:

Y = (A·B + C·D)' - 异或:

Y = A ⊕ B = A'B + AB',两输入相异时,输出为1。 - 同或:

Y = A ⊙ B = AB + A'B',两输入相同时,输出为1。

- 与非:

- 逻辑代数的基本定律和规则:

- 基本定律:0-1律、自等律、互补律、交换律、结合律、分配律、重叠律、反演律(摩根定律)。

- 常用规则:

- 代入规则:任何一个含有变量A的等式,如果将所有出现A的地方都代之以一个函数,则等式仍然成立。

- 反演规则:求一个函数的反函数(或称补函数)。

- 对偶规则:将一个逻辑函数中的变,变,

0变1,1变0,变量不变,得到的新函数为原函数的对偶式。

- 基本逻辑运算:

-

逻辑函数的表示方法

- 真值表:列出所有输入变量组合及其对应的输出值。

- 逻辑函数表达式:由逻辑运算符和变量组合而成的代数式。

- 逻辑图:用逻辑符号表示的逻辑电路图。

- 卡诺图:用于逻辑函数化简的图形工具,特别适合于变量数≤6的情况。

- 波形图:输入和输出信号随时间变化的图形。

-

逻辑函数的化简

(图片来源网络,侵删)

(图片来源网络,侵删)- 化简目的:使用最少的门电路实现,降低成本、提高速度和可靠性。

- 代数化简法:运用逻辑代数定律和规则进行化简,需要技巧和经验。

- 卡诺图化简法:

- 步骤:填卡诺图 → 画包围圈 → 合并最小项 → 写出最简与或式。

- 规则:包围圈要尽可能大;圈数要尽可能少;每个1都必须被圈,且可以被重复圈;不允许“孤立项”。

第二章 逻辑门电路

-

二极管与三极管的开关特性

- 二极管:加正向偏置导通(相当于开关闭合),加反向偏置截止(相当于开关断开)。

- 双极型三极管:工作在饱和区时,相当于开关闭合;工作在截止区时,相当于开关断开,放大区是线性放大区,不是开关工作区。

- MOS管:增强型N沟道MOS管,

V_GS > V_T时导通,V_GS < V_T时截止,是构成CMOS电路的基础。

-

TTL逻辑门电路

- 特点:由双极型三极管构成,速度较快,功耗适中。

- 典型电路:TTL与非门。

- 主要参数:输出高电平

V_OH、输出低电平V_OL、开门电平V_ON、关门电平V_OFF、阈值电压V_TH、噪声容限、扇出系数、传输延迟时间。

-

CMOS逻辑门电路

- 特点:由PMOS和NMOS互补构成,静态功耗极低、抗干扰能力强、电源电压范围宽、集成度高。

- 典型电路:CMOS反相器、CMOS与非门、CMOS或非门。

- 主要参数:与TTL类似,但噪声容限通常更大,输入阻抗极高。

-

逻辑门电路的使用

(图片来源网络,侵删)

(图片来源网络,侵删)- 接口问题:TTL电路与CMOS电路互相驱动时,需要考虑电平匹配和驱动能力问题。

- 集电极开路门和三态门:

- OC门/OD门:输出端可以直接并联,实现“线与”功能,可用于驱动电压高于VCC的负载或实现电平转换。

- 三态门:输出有高电平、低电平、高阻态三种状态,多个三态门输出端可以并联到一条总线上,分时进行数据传输。

第三章 组合逻辑电路

-

组合逻辑电路的特点

- 定义:电路在任意时刻的输出仅取决于该时刻的输入信号,与电路原来的状态无关。

- 结构特点:由各种逻辑门组成,无记忆单元(无触发器),无反馈回路。

-

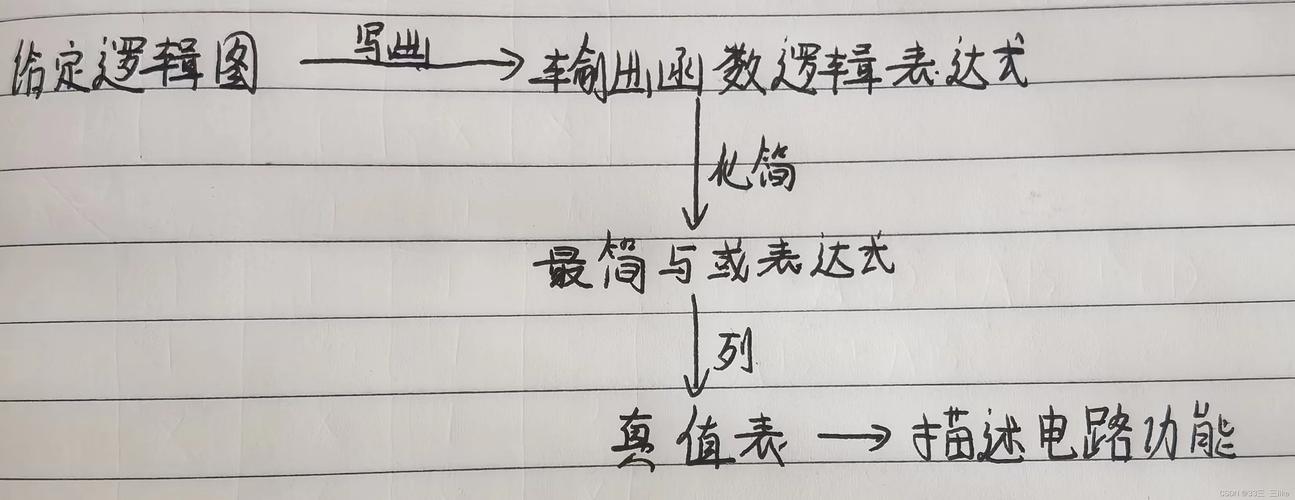

组合逻辑电路的分析与设计

- 分析方法:

- 根据逻辑图,逐级写出输出函数表达式。

- 化简逻辑表达式。

- 列出真值表。

- 描述电路的逻辑功能。

- 设计方法:

- 根据逻辑功能要求,列出真值表。

- 由真值表写出逻辑函数的最小项表达式。

- 化简逻辑函数(通常用卡诺图法)。

- 根据化简后的表达式,画出逻辑电路图。

- 分析方法:

-

常用组合逻辑电路

- 编码器:将输入的信号(如按键、开关状态)编成特定的二进制代码。

- 普通编码器:任何时刻只允许一个输入有效。

- 优先编码器:允许多个输入同时有效,只对其中优先级别最高的输入进行编码。

- 译码器:将二进制代码“翻译”成对应的输出信号(如高/低电平)。

- 二进制译码器:如2-4译码器、3-8译码器、4-

- 编码器:将输入的信号(如按键、开关状态)编成特定的二进制代码。