芯片制造、封装 和 测试,封装和测试紧密相连,通常合称为“封测”,是芯片从晶圆走向成品的关键环节。

第一部分:芯片封装技术

封装技术的核心目标是:保护脆弱的裸芯片、连接芯片与外部电路、散发芯片工作时产生的热量,并便于安装到最终的电子设备中。

封装技术的发展趋势是:小型化、高密度、高性能、高散热、低成本。

传统封装技术

这些是早期和基础的技术,主要用于对成本敏感、性能要求不高的领域。

-

DIP (Dual In-line Package, 双列直插式封装)

(图片来源网络,侵删)

(图片来源网络,侵删)- 特点:有两排平行的引脚,可以直接插入到电路板的孔中。

- 应用:早期的CPU、内存条、逻辑芯片。

- 缺点:体积大,引脚数量有限,无法满足高密度集成需求。

-

SOP/SOIC (Small Outline Package, 小外形封装)

- 特点:引脚从封装两侧引出,呈“鸥翼”或“J”型,体积比DIP小,可以表面贴装在电路板上。

- 应用:逻辑芯片、存储器、电源管理芯片等。

-

QFP (Quad Flat Package, 四侧引脚扁平封装)

- 特点:引脚从封装的四边引出,呈“鸥翼”或“J”型,引脚数量比SOP多得多。

- 应用:需要较多I/O的芯片,如FPGA、ASIC、微控制器。

- 缺点:引脚非常细小,间距小,焊接难度大,且引脚过长会影响高频性能。

先进封装技术

随着摩尔定律放缓,先进封装成为提升芯片性能和集成度的关键,被称为“超越摩尔定律”的核心驱动力。

-

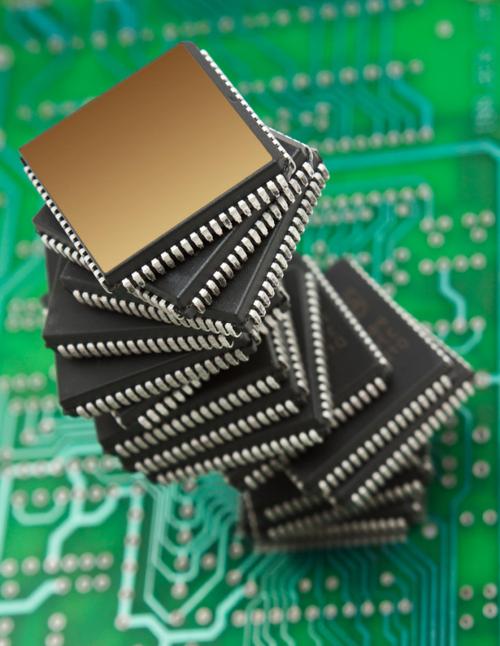

BGA (Ball Grid Array, 球栅阵列封装)

(图片来源网络,侵删)

(图片来源网络,侵删)- 特点:用焊球阵列替代了传统的引脚,焊球位于封装底部,直接连接到电路板的焊盘上。

- 优势:

- 高I/O密度:可以在有限面积内放置更多I/O。

- 更好的电气性能:短而宽的连接线减少了信号干扰和电感。

- 可靠性高:焊球阵列受力均匀,不易虚焊。

- 应用:现代CPU、GPU、FPGA、高性能SoC,是目前主流的封装形式。

-

Flip Chip (倒装芯片)

- 特点:芯片的金属凸点(焊球)直接朝下,倒扣在基板或封装衬底上,通过“回流焊”技术连接。

- 优势:

- 极短的互连路径:信号传输路径最短,信号完整性最好,高频性能极佳。

- 优异的散热性能:芯片产生的热量可以直接通过凸点传导到基板和散热器。

- 应用:几乎所有高性能芯片(如CPU、GPU、移动SoC)都会采用倒装技术。

-

SiP (System in Package, 系统级封装)

- 特点:这不是一种单一的封装形式,而是一种集成理念,它将多个不同功能的裸芯片(如处理器、存储器、射频芯片等)和被动元件(电阻、电容)集成在一个封装体内,形成一个完整的“系统”。

- 优势:

- 高度集成:实现“More than Moore”,功能多样化。

- 缩短设计周期:无需设计复杂的单颗SoC。

- heterogeneous integration (异构集成):可以集成不同工艺、不同材料的芯片。

- 应用:智能手机模块(射频模组、Wi-Fi/蓝牙模组)、智能手表、可穿戴设备。

-

5D / 3D 封装

-

5D 封装

- 特点:多个芯片并排放置在一个硅中介层上,中介层像一座“桥梁”,用高密度布线将这些芯片连接起来,中介层下方再连接到封装基板。

- 优势:解决了芯片间长距离布线的问题,极大地提升了芯片间的带宽和速度。

- 应用:AMD的CPU/GPU组合(如Ryzen Threadripper)、高端FPGA。

-

3D 封装

- 特点:将芯片在垂直方向上堆叠起来,通过TSV(硅通孔,穿透硅片的垂直通道)进行连接。

- 优势:

- 极致的集成度:在极小的空间内容纳更多芯片。

- 极短的互连距离:TSV比传统 wire bond 短几个数量级,性能和功耗优势巨大。

- 应用:高带宽内存、3D NAND闪存(手机存储芯片)、高密度传感器。

-

-

Fan-Out (扇出型封装)

- 特点:芯片的引脚(或称“凸块”)被“扇出”到封装体之外,分布在芯片四周,它不像传统封装那样需要一个基板。

- 优势:

- 更薄、更小:封装尺寸可以做得比传统BGA更小。

- 更好的电气性能:减少了信号传输路径。

- 成本相对较低:工艺流程简化。

- 应用:智能手机应用处理器、射频前端芯片。

第二部分:芯片测试技术

测试贯穿于芯片生产的全过程,主要分为两个阶段:晶圆测试 和 封装后测试。

晶圆测试

在晶圆制造完成后、切割之前,对晶圆上的每一个裸芯片进行测试。

-

目的:

- 尽早发现缺陷:在晶圆阶段就筛选出不合格的芯片,避免将它们封装起来,从而节省大量的封装和测试成本。

- 提供数据反馈:测试结果可以帮助工程师分析制造工艺中的问题,提高良率。

-

主要技术:

- CP测试:通常使用探针卡,上面有成千上万个微小的探针,精准地接触到芯片焊盘,对芯片进行功能测试、逻辑测试和部分模拟测试。

- WAT (Wafer Acceptance Test, 晶圆接受测试):主要测试制造工艺中的关键参数,如晶体管的阈值电压、氧化层厚度、电阻/电容值等,确保工艺本身是稳定和合格的。

封装后测试

将晶圆切割、封装成独立的芯片后,进行的最终测试,确保芯片完全符合设计规格。

-

目的:

- 最终质量保证:确认封装后的芯片功能、性能和可靠性都达标。

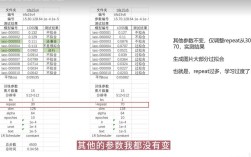

- 分级和筛选:根据测试结果对芯片进行分级(如Bin Sort),例如将性能最好的芯片标记为“超频版”或用于高端产品。

-

主要技术:

- FT测试:这是最核心的测试,使用测试插座将封装好的芯片连接到自动测试设备上。

- 功能测试:验证芯片的逻辑功能是否正确,例如运行一个“Hello World”程序。

- 直流参数测试:测试电压、电流、功耗等是否符合规格。

- 交流参数测试:测试芯片的时序、频率、带宽等性能指标。

- 可靠性测试:模拟芯片在极端或长期使用条件下的表现,以确保其寿命和稳定性,测试项目包括:

- HTOL (High Temperature Operating Life, 高温工作寿命测试):在高温下满负荷运行,加速老化。

- THB (Temperature Humidity Bias, 温湿度偏压测试):高温高湿环境下加电,测试抗腐蚀能力。

- TCT (Temperature Cycling Test, 温度循环测试):在极低和极高温度之间反复切换,测试抗热应力能力。

- Drop Shock (跌落冲击测试):模拟芯片在跌落或受到外力冲击时的表现。

- 最终测试:在出厂前进行100%的测试,确保每一颗交付给客户的芯片都是合格的。

- FT测试:这是最核心的测试,使用测试插座将封装好的芯片连接到自动测试设备上。

| 类别 | 关键技术 | 核心目标/特点 | 主要应用领域 |

|---|---|---|---|

| 封装技术 | 传统封装 | DIP, SOP, QFP | 成本敏感、低密度应用 |

| 先进封装 | BGA (主流)、Flip Chip (高性能基础)、SiP (系统集成)、5D/3D (超高带宽)、Fan-Out (小型化) | CPU/GPU/FPGA/SoC/移动设备/存储 | |

| 测试技术 | 晶圆测试 | CP测试 (功能筛选)、WAT测试 (工艺监控) | 晶圆制造阶段,降低成本 |

| 封装后测试 | FT测试 (功能/性能验证)、可靠性测试 (寿命/稳定性验证) | 封装后阶段,质量保证 |

封装和测试技术是半导体产业中至关重要的一环,它们共同决定了芯片的性能、成本、可靠性和市场竞争力,随着芯片设计越来越复杂,封测技术的重要性与日俱增,成为了各大半导体厂商和封测厂商竞争的焦点。