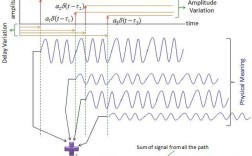

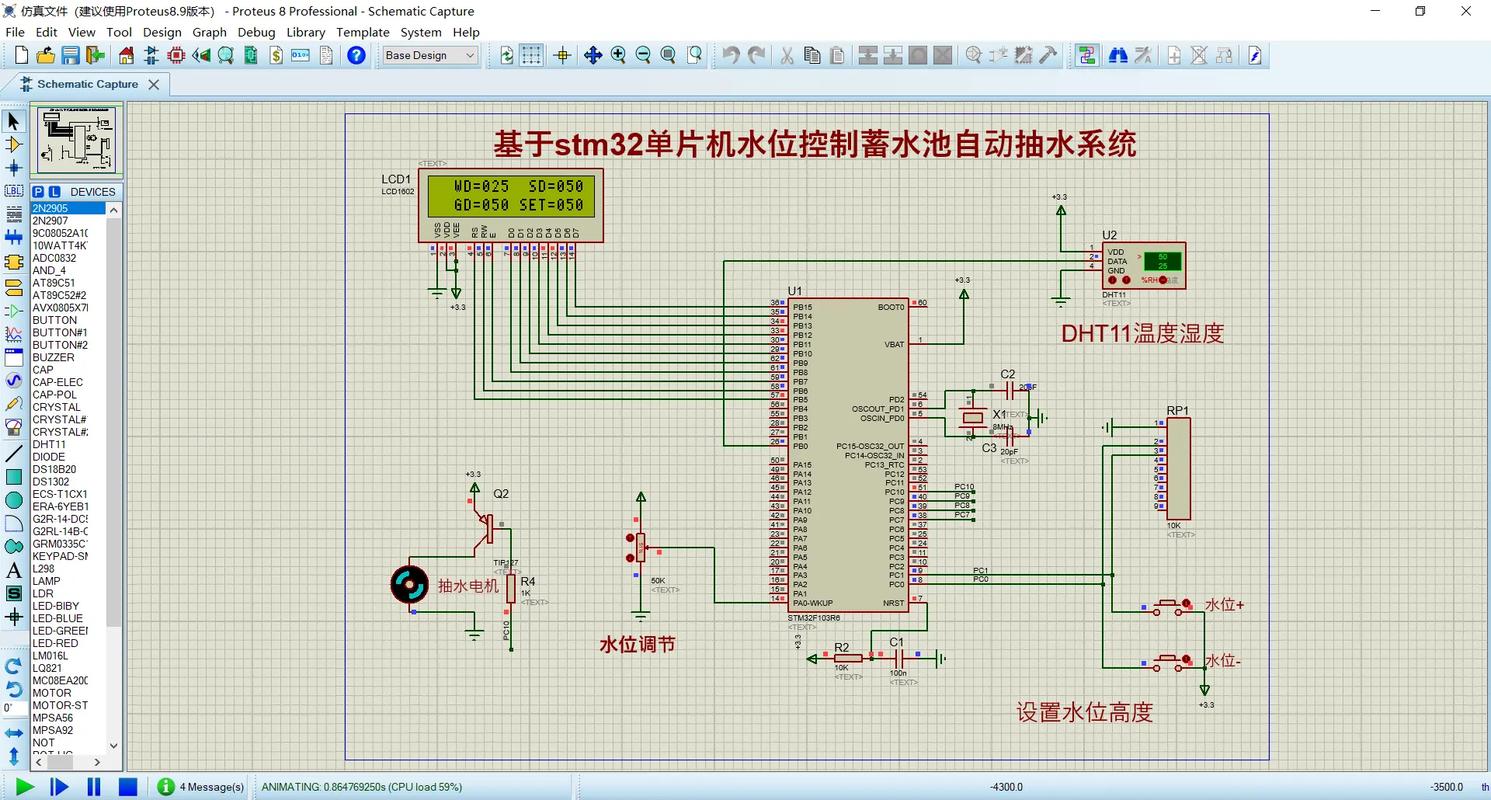

FPGA中的流水技术是一种通过将复杂的计算任务分解为多个连续的子任务,并在不同时钟周期内并行处理这些子任务,从而提高系统吞吐量和运行效率的关键设计方法,其核心思想类似于工厂流水线,每个子任务由独立的处理单元(称为“流水线级”)完成,数据在各级之间按固定顺序传递,通过重叠执行不同阶段的任务,显著减少整体处理延迟,在FPGA中,流水技术的实现依赖于硬件描述语言(如Verilog或VHDL)对逻辑模块的时序划分,以及寄存器对各级之间数据的暂存和同步,确保数据在时钟驱动下稳定流动。

流水技术的优势主要体现在三个方面:一是提高吞吐量,理想情况下,每个时钟周期都能完成一个任务,而非传统串行方式的N个时钟周期完成N个任务(N为流水线级数);二是降低组合逻辑延迟,通过将长路径拆分为多个短路径,满足FPGA的时序约束,提高系统工作频率;三是资源利用率优化,各级逻辑可复用FPGA中的查找表(LUT)、触发器等资源,避免重复设计,一个32位乘法器若采用单级实现,组合逻辑延迟可能较大;若拆分为5级流水线(如部分积生成、累加、对齐等),每级仅需处理部分运算,可将延迟分散到多个时钟周期,支持更高频率运行。

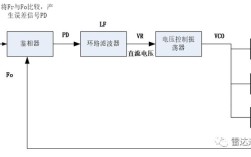

流水线设计的关键步骤包括任务划分、寄存器插入和时序优化,任务划分需遵循“负载均衡”原则,确保各级逻辑复杂度相近,避免某级成为性能瓶颈;寄存器插入则在各级输出端添加触发器,暂存中间结果,防止毛刺传播;时序优化需通过FPGA开发工具(如Vivado或Quartus)的时序分析,调整布局布线以减少时钟偏斜(Skew)和建立/保持时间违规,流水线还需处理“流水线气泡”(Bubble)问题,如分支指令或数据依赖导致的空转周期,可通过旁路技术(Bypassing)或乱序执行(Out-of-Order Execution)缓解,但FPGA中通常以简单插入空闲周期的方式实现,以控制设计复杂度。

流水技术的分类可根据流水线级数、功能或数据流特征划分,按级数分为单级、多级和超长流水线(如GPU中的上千级);按功能分为算术流水线(如DSP模块)、指令流水线(如CPU取指-译码-执行)和存储器流水线(如DDR读写);按数据流分为线性流水线(顺序执行)和非线性流水线(反馈或迭代结构),在FPGA中,DSP48E等硬核模块常被用于构建高效算术流水线,而BRAM可通过双端口配置实现存储器流水线,支持并行读写操作。

尽管流水技术优势显著,但也面临设计挑战,首先是面积开销,每级流水线需插入寄存器,会增加触发器资源消耗,例如N级流水线可能比单设计多用(N-1)*寄存器数量;其次是时序收敛难度,高频下寄存器到寄存器的路径需严格约束,跨时钟域(CDC)设计还需同步器避免亚稳态;最后是调试复杂性,流水线中的数据需通过ILA(集成逻辑分析仪)逐级追踪,故障定位难度高于非流水设计,实际设计中需在性能、资源和可调试性之间权衡,例如对低延迟任务采用浅流水线,对高吞吐任务采用深流水线。

相关问答FAQs:

Q1: 流水技术与并行计算有何区别?

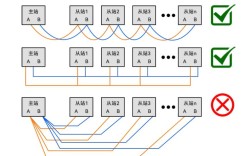

A1: 流水技术是“时间并行”的体现,通过重叠不同任务的执行阶段提高吞吐量,而并行计算(如FPGA中的多实例)是“空间并行”,通过同时复制多个处理单元执行相同或不同任务,流水线乘法器在时间上分步完成乘法,而并行乘法器则同时使用多个乘法器单元计算不同乘法结果,流水技术更适合单任务拆分,并行计算适合多任务并发。

Q2: 如何减少FPGA流水线中的气泡?

A2: 气泡主要由数据依赖或控制分支导致,可通过以下方法减少:①数据前推(Forwarding),将前级结果直接旁路到后级输入,避免等待寄存器更新;②分支预测,提前执行可能路径的任务,若预测错误则刷新流水线;③任务重排,调整算法顺序减少依赖;④插入空闲指令(如NOP),在分支延迟期填充气泡,但FPGA中通常以简化设计为主,避免过度复杂化控制逻辑。