锁相频率合成技术是一种基于锁相环(PLL)电路的高精度频率合成方法,通过相位反馈控制技术实现对输出频率的稳定、精确调节,该技术结合了频率合成的高效性和锁相环的高稳定性,在现代通信、雷达、导航、测量仪器等领域得到广泛应用,成为电子系统中不可或缺的核心技术之一。

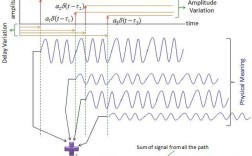

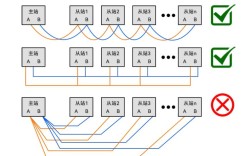

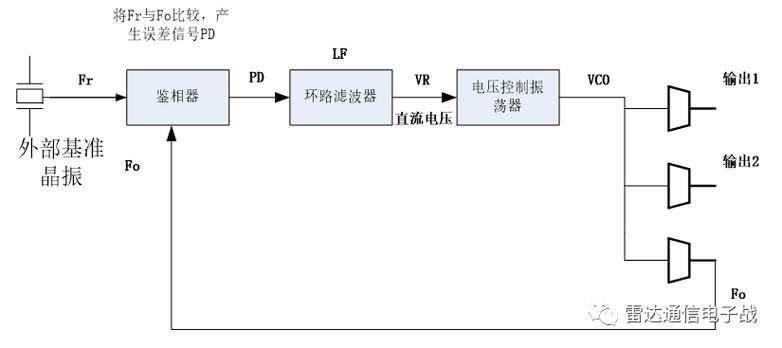

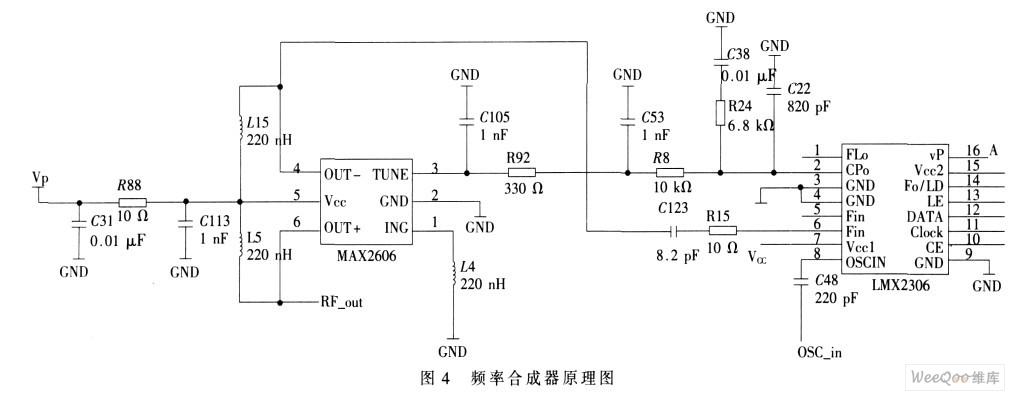

锁相频率合成技术的基本原理是利用锁相环的相位跟踪特性,将压控振荡器(VCO)的输出频率锁定到参考频率的整数倍或分数倍上,其核心系统通常由鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和分频器(Divider)四部分组成,鉴相器用于比较参考信号与反馈信号的相位差异,输出误差电压;环路滤波器对误差电压进行平滑处理,滤除高频噪声并决定环路动态响应;压控振荡器根据控制电压输出相应频率的信号;分频器则将VCO输出频率按比例降低后送回鉴相器,形成闭合反馈回路,通过调整分频比,即可实现不同频率点的输出。

根据分频器的实现方式,锁相频率合成技术可分为整数分频频率合成和小数分频频率合成两大类,整数分频频率合成技术结构简单,成本低,但频率分辨率受限于参考频率,无法实现连续小步进调谐,当参考频率为10kHz时,频率分辨率至少为10kHz,难以满足高精度通信系统的需求,小数分频频率合成技术通过引入累加器和伪随机序列发生器,实现了分数倍频功能,使频率分辨率突破参考频率的限制,在相同参考频率下,可实现1Hz甚至更小的频率步进,显著提高了频率合成器的灵活性和精度,但该技术会引入小数杂散,需通过高级算法和电路设计进行抑制。

锁相频率合成技术的性能指标主要包括频率分辨率、频率切换速度、相位噪声、杂散抑制和功耗等,频率分辨率指最小可调谐频率间隔,小数分频技术可轻松达到μHz量级;频率切换速度反映环路从锁定到稳定的时间,通常为微秒至毫秒级;相位噪声是衡量输出信号短期稳定性的关键指标,主要受VCO和环路滤波器设计影响,典型值可达-100dBc/Hz@10kHz;杂散抑制则要求非基频信号功率低于基频一定分贝数,一般需大于60dB,这些指标在不同应用场景中需根据需求进行权衡,例如通信系统侧重相位噪声和杂散抑制,雷达系统则更关注频率切换速度。

与直接数字频率合成(DDS)和直接模拟频率合成技术相比,锁相频率合成技术具有显著优势,DDS虽然频率分辨率极高且切换速度快,但输出频率受限于时钟频率,且杂散抑制能力较弱;直接模拟频率合成器速度快,但结构复杂、成本高、体积大,锁相频率合成技术通过合理设计环路参数,可在频率范围、分辨率、稳定性和成本之间取得良好平衡,在5G基站中,锁相频率合成器结合小数分频技术和低噪声VCO,可同时满足亚赫兹级分辨率和-110dBc/Hz的相位噪声要求。

随着集成电路技术的发展,锁相频率合成技术正向着更高集成度、更低功耗和智能化方向发展,采用CMOS工艺的片上系统(SoC)解决方案将鉴相器、环路滤波器、VCO和控制逻辑集成在单一芯片上,大幅减小了系统体积和功耗,现代射频SoC中的锁相频率合成器功耗可低至10mW以下,同时支持GHz频段输出,自适应环路带宽控制、数字辅助校准等技术的引入,进一步提升了频率合成器在温度变化和电源波动环境下的稳定性,满足了移动设备和物联网终端对高性能频率源的需求。

以下是锁相频率合成技术关键参数对比表:

| 参数类型 | 整数分频频率合成 | 小数分频频率合成 | 直接数字频率合成 |

|---|---|---|---|

| 频率分辨率 | ≥参考频率 | μHz量级 | μHz~nHz量级 |

| 频率切换速度 | 100μs~1ms | 50μs~500μs | <10ns |

| 相位噪声典型值 | -90dBc/Hz@10kHz | -110dBc/Hz@10kHz | -80dBc/Hz@10kHz |

| 杂散抑制 | >60dB | >70dB(需优化) | >40dB |

| 功耗(GHz频段) | 20~50mW | 15~40mW | 50~200mW |

| 集成度 | 高 | 高 | 中等 |

相关问答FAQs:

Q1:锁相频率合成技术中的小数分频如何实现频率分辨率的提升?

A:小数分频技术通过在N和N+1两个整数分频状态之间动态切换来实现平均分频比为非整数值,具体而言,采用累加器和小数模值控制电路,根据小数部分决定N和N+1分频状态的占空比,分频比10.3可通过7次N分频和3次N+1分频的组合实现,平均分频频率为10.3倍参考频率,这种技术使频率分辨率突破参考频率限制,但需通过噪声整形技术(如Σ-Δ调制)抑制因分频比切换引入的小数杂散。

Q2:如何优化锁相频率合成器的相位噪声性能?

A:优化相位噪声需从环路设计和器件选型两方面入手,在环路设计上,应合理选择环路带宽,使其低于参考频率但高于VCO噪声拐角频率,以平衡鉴相器噪声和VCO噪声的影响;采用高阶环路滤波器可提高高频抑制能力,但需避免过度增加环路响应时间,在器件选型上,优选低噪声压控振荡器(如介电振荡器DRO)、高鉴相灵敏度鉴相器和低电阻环路滤波器,电源去耦、屏蔽隔离和PCB布局优化等工艺措施对降低相位噪声也至关重要。