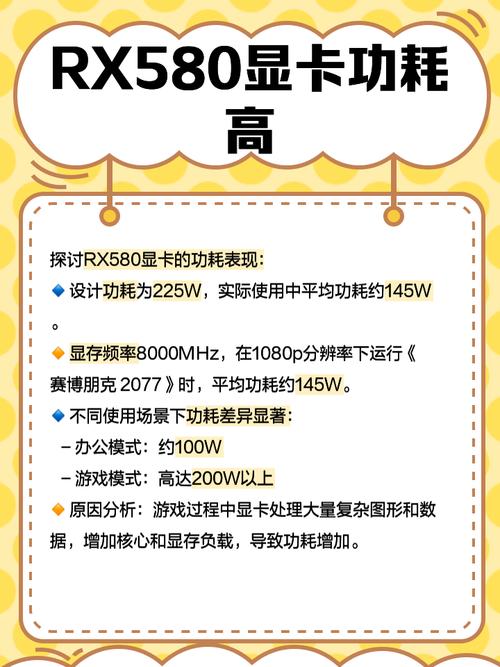

我们需要明确几个核心概念,因为“功耗”和“能量”在日常使用中常被混用,但在技术领域有明确的区别:

- 功耗: 指的是单位时间内消耗的能量,单位是瓦特,它衡量的是设备的“电费账单”或对电源的即时压力。功耗 = 电压 × 电流。

- 能量: 指的是完成某项任务所消耗的总电量,单位是焦耳,它衡量的是完成特定工作(如计算一次、发送一次数据)所消耗的资源总和。能量 = 功耗 × 时间。

理解这两者的区别至关重要:

- 一个低功耗的设备如果长时间运行,其总能量消耗可能很高。

- 一个高功耗的设备如果只在极短时间内完成任务,其总能量消耗可能很低。

低能量-功耗设计的核心目标不仅仅是降低“瓦特数”,更是优化完成特定任务的“焦耳数”。

低功耗设计的基本原理

所有低功耗技术都围绕着以下三个基本物理公式展开:

-

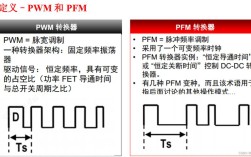

动态功耗: $P_{dynamic} = C \times V^2 \times f$

(图片来源网络,侵删)

(图片来源网络,侵删)C: 负载电容V: 电源电压f: 工作频率- 这是CMOS电路最主要的功耗来源,主要由电路状态翻转(充放电)引起。

-

静态功耗: $P{static} = V \times I{leakage}$

V: 电源电压I_{leakage}: 漏电流,即使在晶体管关闭时也存在。- 随着工艺尺寸缩小,漏电流问题越来越严重。

-

短路功耗: $P{short-circuit} = V \times I{short-circuit}$

在信号翻转瞬间,电源和地之间会存在一个短暂的直接通路,产生电流,在现代设计中,这部分功耗通常被包含在动态功耗中估算。

从公式可以看出,降低电压是降低功耗最有效的方法(二次方关系),但降低电压会降低电路速度,因此需要与频率等其他因素进行权衡。

低功耗设计技术的层次化方法

低功耗设计技术贯穿于整个电子系统设计流程,从系统级到电路级,层层递进,通常分为两大类:动态功耗管理和面向低功耗的设计。

(一) 动态功耗管理

这类技术通过动态地调整工作电压和频率,来匹配当前的计算负载,从而在空闲或低负载时节省能量。

-

动态电压与频率调节

- 原理: 根据当前的计算任务需求,动态调整处理器的核心电压和工作频率,当处理简单任务或空闲时,降低电压和频率;当处理高负载任务时,提高电压和频率。

- 实现: 需要硬件支持(如可调压的电源管理单元、支持DVFS的CPU)和软件配合(如操作系统内核的 governors,如

ondemand,conservative)。 - 优点: 能在性能和功耗之间取得极佳的平衡,对用户体验影响小。

- 应用: 几乎所有现代移动处理器、服务器CPU。

-

电源门控

- 原理: 在芯片内部或模块级别,通过一个“开关”(通常是MOS管)来切断整个功能模块或部分电路的电源,当模块不工作时,将其完全断电,使其功耗降至接近零。

- 实现: 需要专门的“电源门控单元”和复杂的时序控制逻辑来确保唤醒时的正确性。

- 优点: 能消除模块的静态漏电流,节能效果显著。

- 应用: 关闭不使用的CPU核心、GPU、缓存模块、外设接口等。

-

时钟门控

- 原理: 与电源门控类似,但它控制的是时钟信号,通过“与门”等逻辑,在模块不工作时停止向其提供时钟脉冲,由于没有翻转,动态功耗被消除,但静态漏电依然存在。

- 实现: 相对电源门控更简单,通常由综合工具自动插入。

- 优点: 实现简单,能显著减少不必要的动态功耗。

- 应用: RTL设计阶段的标准实践,用于关闭暂时不工作的寄存器和时序逻辑。

-

自适应电压调节

- 原理: 这是DVFS的进一步发展,由于芯片内部不同位置、不同工艺角下的电压需求存在微小差异,AVR可以为每个核心或模块提供其刚好够用的最小电压,而不是用一个统一的电压。

- 优点: 进一步降低了电压裕度带来的能量浪费。

- 应用: 先进的片上系统。

(二) 面向低功耗的设计

这类技术是在设计之初就通过架构、逻辑和电路的优化来从源头上降低功耗。

-

系统级/架构级

- 异构计算: 将不同类型的处理器核心集成在一个芯片上,如“big.LITTLE”架构(ARM big.LITTLE),将高性能的“大核”用于计算密集型任务,将高能效的“小核”用于日常任务,这样可以根据任务类型选择最合适的核心,而不是一直用高性能核心。

- 专用加速器: 针对特定算法(如AI推理、视频编解码)设计专用的硬件电路,专用硬件通常比通用CPU能效比高出几个数量级。

- 近似计算: 在某些应用中(如机器学习、多媒体处理),不需要100%精确的计算结果,通过故意降低计算精度(例如用8位浮点数代替32位浮点数),可以显著减少数据位宽、计算复杂度和数据移动量,从而大幅降低功耗和面积。

- 存储器优化: 存储器访问是主要的能耗来源之一,技术包括:使用多级缓存、采用低功耗的SRAM/DRAM技术、数据压缩以减少访问量、智能预取等。

-

逻辑/RTL级

- 门控时钟: 如前所述,这是RTL设计中的基本手段。

- 逻辑优化: 使用逻辑综合工具进行优化,减少不必要的逻辑门翻转,使用“多路选择器”代替“与或非”门在某些场景下更节能。

- 异步设计: 不使用全局时钟,而是通过数据流本身来驱动电路,这从根本上消除了时钟树功耗和时钟偏移问题,能效非常高,但设计极其复杂,尚未成为主流。

- 总线编码: 在数据总线上传输数据前进行编码,减少总线上的翻转位数,使用“总线反转”技术,当连续传输的数据有多个位变化时,可以翻转整个总线的极性,从而减少翻转次数。

-

物理/电路级

- 电源/地网络优化: 设计低电阻、低电感的电源和地网络,确保电压稳定,减少IR Drop和EMI,从而降低动态功耗。

- 晶体管尺寸优化: 对关键路径上的晶体管进行 upsizing 以提高速度(从而可以降低频率),对非关键路径的晶体管进行 downsizing 以减小电容(从而降低动态功耗)。

- 多阈值电压 工艺: 在芯片制造时,为不同晶体管提供不同的阈值电压,高阈值电压晶体管漏电小但速度慢,用于非关键路径;低阈值电压晶体管速度快但漏电大,用于关键路径,这是一种面积、功耗和速度之间的权衡。

- 近阈值/亚阈值计算: 让晶体管工作在接近或低于其阈值电压的区域,虽然速度极慢,但漏电流和动态功耗都极低,对于超低功耗的物联网设备非常有效。

设计流程中的低功耗策略

现代芯片设计遵循一套标准化的低功耗流程,由 UPF (Unified Power Format) 标准定义。

- 功耗分析与建模: 在设计早期,使用工具对功耗进行快速估算,为架构决策提供依据。

- 低功耗架构定义: 使用UPF文件定义电源域、电源开关、隔离单元、电平转换器等低功耗组件。

- 低功耗综合: 综合工具根据UPF约束,自动插入时钟门控和电源门控逻辑。

- 物理实现: 在布局布线阶段,确保电源网络和时钟网络的完整性,并处理由电源开关引入的时序问题。

- 功耗验证: 在最终流片前,使用功耗仿真工具(如UPF-aware仿真)验证低功耗功能是否正确,确保唤醒/休眠流程无误。

- 后功耗分析: 在设计完成后,进行精确的功耗分析,包括动态功耗、静态功耗和IR Drop分析,确保功耗满足设计目标。

低能量-功耗设计是一个系统性工程,没有单一的“银弹”,它需要设计师在不同层次上做出权衡和优化:

| 层次 | 核心思想 | 关键技术 | 目标 |

|---|---|---|---|

| 系统/架构 | 按需分配,避免过度设计 | 异构计算、专用加速器、近似计算 | 在性能和功耗间找到最佳平衡点 |

| 逻辑/RTL | 减少不必要的活动 | 门控时钟、逻辑优化、异步设计 | 从源头上降低翻转次数和开关活动 |

| 物理/电路 | 优化底层器件和连接 | 多阈值电压、电源/地网络优化、近阈值计算 | 在工艺和物理层面实现极致能效 |

| 运行时管理 | 动态适应负载变化 | DVFS、电源门控、时钟门控 | 在软件和硬件协同下,按需调整工作状态 |

未来的趋势是系统级和AI驱动的功耗管理,即利用机器学习来预测工作负载,并做出更智能、更前瞻性的电压和频率调整,从而将能量效率推向新的高度。