EDA技术及应用 答辩PPT内容框架

答辩PPT结构建议 (约15-20分钟)

- 封面 (1张)

- 目录/议程 (1张)

- 第一部分:绪论 - 为什么需要EDA? (2-3张)

- 第二部分:EDA技术核心详解 (3-5张)

- 第三部分:EDA技术应用实践 (3-5张) - (这是重点,展示你的项目)

- 第四部分:挑战与未来展望 (1-2张)

- 第五部分:总结与致谢 (1-2张)

- Q&A环节 (准备充分)

各部分详细内容与讲稿要点

Slide 1: 封面

- EDA技术及应用

- (可选): 以[你的具体项目名称,如“基于FPGA的图像处理系统设计”]为例

- 答辩人: 你的名字

- 指导老师: 老师姓名

- 日期: 答辩日期

Slide 2: 目录

- 简要列出PPT的几个主要部分,让评委对你的整体结构有清晰的预期。

-

绪论:背景与意义

-

EDA技术核心:从概念到流程

-

应用实践:[你的项目名称]详解

-

挑战与未来展望

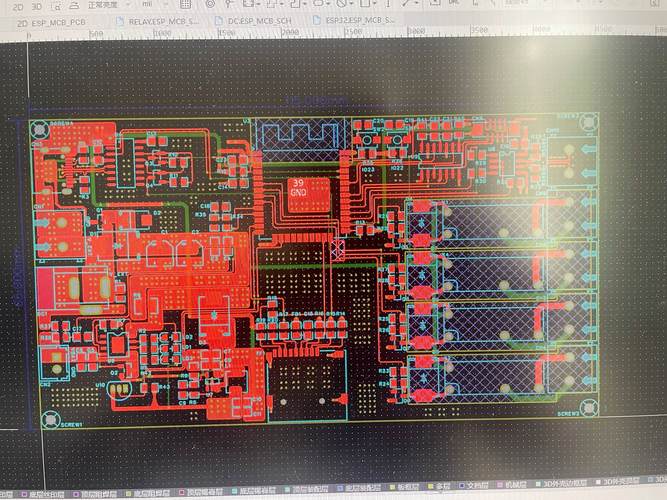

(图片来源网络,侵删)

(图片来源网络,侵删) -

总结与致谢

-

第一部分:绪论 - 为什么需要EDA? (2-3张)

Slide 3: 课题背景与意义

- 摩尔定律的延续: 随着集成电路工艺进入7nm、5nm甚至更先进节点,晶体管数量呈指数级增长,设计复杂度呈爆炸式增长。

- “设计鸿沟” (Design Gap): 芯片制造能力的提升速度远快于人工设计能力的提升,没有EDA工具,现代芯片设计几乎不可能完成。

- EDA的价值: EDA是芯片产业的“基石”和“使能器”,它将工程师的抽象设计(如代码)转化为物理上可制造的版图,是连接“设计”与“制造”的桥梁。

- 配图: 摩尔定律曲线图、一颗巨大的芯片、EDA工具将代码转换为芯片的示意图。

Slide 4: EDA的定义与范畴

- 定义: Electronic Design Automation,电子设计自动化,利用计算机辅助工具,完成超大规模集成电路(VLSI)从功能定义、逻辑设计、物理设计到验证、测试的整个过程。

- 核心范畴 (可用流程图展示):

- 前端设计: RTL设计、功能仿真、逻辑综合

- 后端设计: 布局布线、物理验证、版图生成

- 验证与测试: 形式验证、静态时序分析、可测性设计

- 讲稿要点: “EDA不是一个单一的工具,而是一个涵盖了芯片设计全生命周期的工具链生态系统。”

第二部分:EDA技术核心详解 (3-5张)

Slide 5: EDA典型设计流程

- 这是本部分的核心,用一张清晰的流程图展示。

- 规格定义: 明确芯片的功能、性能、功耗、面积等指标。

- RTL设计: 使用Verilog/VHDL等硬件描述语言进行行为级和寄存器传输级设计。

- 功能仿真: 验证RTL代码的逻辑功能是否正确,与设计规格一致。

- 逻辑综合: 将RTL代码转换为由标准逻辑门(与、或、非等)组成的门级网表。

- 物理设计: 包括布局、布线、时钟树综合等,将网表转化为实际的几何版图。

- 后端验证: 进行时序分析、功耗分析、物理规则检查等,确保设计在物理上是可实现的。

- 讲稿要点: “这是一个从‘做什么’到‘怎么做’再到‘如何造出来’的迭代和精炼过程。”

Slide 6: 核心EDA工具介绍

- 列举业界主流的EDA工具,并简要说明其作用。

- 仿真器: Synopsys VCS, Cadence Xcelium (用于功能仿真)

- 综合工具: Synopsys Design Compiler, Cadence Genus (用于逻辑综合)

- 布局布线工具: Synopsys IC Compiler, Cadence Innovus (用于物理设计)

- 验证工具: Synopsys Formality (形式验证), Cadence Joules (功耗分析)

- 讲稿要点: “这些工具构成了EDA产业的巨头,它们共同保证了设计的效率和成功率。”

第三部分:应用实践:[你的项目名称]详解 (3-5张) - (重点!)

Slide 7: 项目概述

- 项目名称: [基于FPGA的简易图像边缘检测系统设计]

- 设计目标: 实现一个能够对输入图像进行实时边缘检测的硬件系统。

- 实现平台: Xilinx Zynq-7000 SoC (或你使用的具体FPGA开发板)。

- 技术路线: 采用Verilog HDL进行RTL设计,使用Vivado EDA工具进行综合、实现与验证。

- 讲稿要点: “我将通过我的具体项目,展示EDA技术是如何被实际应用的。”

Slide 8: 项目设计流程与EDA工具链

- 将你的项目过程与上一页的EDA典型流程图对应起来,展示你如何应用了EDA。

- 设计与建模: 使用Verilog编写Sobel边缘检测算法的RTL代码。

- 功能仿真: 使用ModelSim或Vivado自带的仿真器,编写Testbench,验证算法逻辑的正确性。

- 逻辑综合: 使用Vivado的综合器,将Verilog代码转换为门级网表。

- 实现与布局布线: 使用Vivado的Implementation工具,进行翻译、映射、布局和布线,生成最终的比特流。

- 时序与物理验证: 查看时序报告,确保设计满足FPGA的时序约束。

- 配图: Vivado工程截图、仿真波形图、布局布线后的资源占用报告。

Slide 9: 关键技术实现与成果展示

- 展示你的项目亮点和最终成果。

- 关键技术点:

- 如何处理图像数据流?(双端口RAM缓存)

- 如何优化Sobel运算的并行度?(流水线设计)

- 如何处理边界像素问题?

- 成果展示:

- 仿真波形图: 清晰地展示输入和输出信号的对应关系。

- 板级运行照片: 展示开发板、摄像头和显示器。

- 结果对比图: 左边是原始图像,右边是FPGA处理后的边缘检测图像。

- 资源占用报告: 展示项目占用了FPGA多少LUT、FF、BRAM等资源。

- 性能分析: 处理速度达到XX帧/秒,满足实时性要求。

- 关键技术点:

- 讲稿要点: “通过这个项目,我不仅掌握了Verilog RTL设计,更重要的是,我亲身体验了如何使用EDA工具(如Vivado)完成从代码到硬件的全过程,并成功验证了设计。”

第四部分:挑战与未来展望 (1-2张)

Slide 10: 当前EDA面临的挑战

- 先进工艺的挑战: 3nm/2nm工艺下的物理效应(如DTCO/TCO)变得异常复杂。

- AI与芯片设计的融合: 如何利用AI来优化EDA流程本身(如AI驱动的布局布线)。

- 开源EDA的崛起: C++、OpenROAD等开源工具对商业EDA生态的冲击与机遇。

- 安全性与IP保护: 硬件木马、设计窃取等问题日益突出。

- 讲稿要点: “EDA技术本身也在不断演进,以应对摩尔定律放缓和新兴技术带来的新挑战。”

Slide 11: EDA的未来发展趋势

- 面向Chiplet的设计: EDA工具需要支持异构集成和2.5D/3D堆叠。

- “数据驱动”的EDA: 利用大数据和机器学习进行预测性分析和设计优化。

- 云原生EDA: 将EDA工具部署在云端,提供更灵活、弹性的设计环境。

- RISC-V生态的EDA支持: 随着RISC-V的兴起,需要更完善的EDA工具链。

- 讲稿要点: “EDA将更加智能化、平台化和云化,继续支撑着整个半导体产业的发展。”

第五部分:总结与致谢 (1-2张)

Slide 12: 总结

- 回顾: 简要回顾EDA的定义、核心流程和重要性。

- 实践: 总结通过[你的项目]对EDA技术的应用和理解,达到了预期目标。

- 展望: 对EDA技术的未来发展表示期待。

- 讲稿要点: “EDA是现代集成电路设计的灵魂,通过本次课题的学习与实践,我深刻理解了EDA技术对于推动科技创新的巨大价值。”

Slide 13: 致谢

- 衷心感谢我的指导老师[老师姓名]的悉心指导!

- 感谢各位评委老师在百忙之中抽出时间参加我的答辩!

- 感谢所有帮助过我的同学和朋友们!

- 讲稿要点: “我的汇报到此结束,谢谢大家!恳请各位老师批评指正。”

Q&A环节准备

- 预测问题:

- 基础概念题: “请解释一下逻辑综合和布局布线的区别与联系?” “什么是静态时序分析?”

- 项目深挖题: “在你的项目中,你遇到了最大的挑战是什么?你是如何用EDA工具解决它的?” “如果给你更多时间,你会在设计上做哪些优化?”

- 行业视野题: “你认为开源EDA工具(如OpenROAD)对商业EDA巨头会构成多大威胁?” “你对Chiplet技术对未来EDA工具链的影响怎么看?”

- 个人反思题: “通过这个项目,你最大的收获是什么?” “你觉得自己在EDA技术方面还有哪些不足?”

- 回答技巧:

- 先总后分: 先给出一个核心观点,再展开论述。

- 结合实例: 尽量用你项目中的例子来回答问题,显得更真实可信。

- 诚实谦虚: 遇到不会的问题,坦诚表示“这个问题我研究得还不够深入,我的理解是……”,千万不要不懂装懂。

- 控制时间: 回答问题要言简意赅,突出重点。

祝你答辩顺利,取得优异成绩!