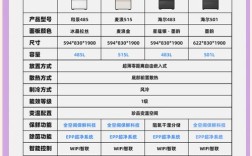

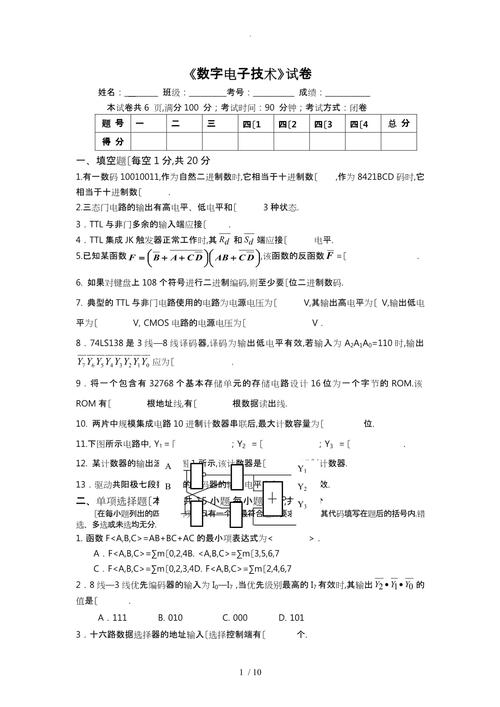

试题分为 选择题、填空题、分析设计题 和 综合应用题 四个部分,并附有详细的参考答案。

《数字电子技术基础》期末考试模拟试题

考试时间:120分钟 总分:100分

班级:__ 学号:__ 姓名:__ 成绩:__

选择题(每题2分,共20分)

-

与十进制数56等值的8421BCD码是。 A. 01010110 B. 01110000 C. 01111000 D. 00110110

-

逻辑函数 F(A,B,C) = Σm(0, 3, 5, 7) 的最简“与或”表达式是。 A. A'B'C + A'BC + ABC B. C + AB C. (A+B)C D. A'C + BC

(图片来源网络,侵删)

(图片来源网络,侵删) -

一个TTL反相器(非门)的输入端通过一个电阻接地,该电阻阻值为10kΩ,此时该门电路的逻辑状态为。 A. 逻辑0 B. 逻辑1 C. 高阻态 D. 不确定

-

下列逻辑门电路中,可以实现“线与”功能的是。 A. TTL与非门 B. CMOS或非门 C. 集电极开路门 D. 三态门

-

对于JK触发器,当 J=K=1 时,每来一个时钟脉冲,触发器的状态将。 A. 保持不变 B. 置1 C. 置0 D. 翻转(即取反)

-

一个4位右移移位寄存器,初始状态为

0000,若串行输入端输入数据为1011,经过4个时钟脉冲作用后,寄存器中的状态为。 A.1011B.1101C.1110D.0111 (图片来源网络,侵删)

(图片来源网络,侵删) -

一个8位D/A转换器,其参考电压VREF = 5V,当输入数字量为

10000000时,其输出电压约为。 A. 2.5V B. 5V C. 1.25V D. 3.75V -

欲设计一个将4位二进制代码转换为4位格雷码的组合逻辑电路,应选用。 A. 译码器 B. 编码器 C. 数据选择器 D. 数值比较器

-

同步时序逻辑电路和异步时序逻辑电路的根本区别在于。 A. 是否有触发器 B. 是否有组合逻辑电路 C. 所有触发器是否使用同一个时钟脉冲 D. 输出是否与输入有关

-

下列器件中,属于时序逻辑电路的是。 A. 编码器 B. 数据选择器 C. 计数器 D. 译码器

填空题(每空1分,共20分)

- 数字电路中,基本的逻辑关系有与逻辑、__逻辑和__逻辑。

- 在数字系统中,常用的数制有二进制、__和__。

- 逻辑函数的表示方法主要有真值表、__、__和卡诺图。

- 三态门的三种输出状态分别是:高电平、低电平和__。

- 触发器是具有记忆功能的逻辑电路,它能够存储__位二进制信息。

- 一个n位的二进制计数器,其模值为__,能够计数的最大十进制数是__。

- 组合逻辑电路的特点是:任意时刻的输出仅仅取决于该时刻的__,与电路原来的状态__。

- 构成时序逻辑电路的基本部分是组合逻辑电路和__。

- A/D转换过程包括四个步骤:采样、保持、__和__。

- 一个8位D/A转换器,其分辨率是__;若参考电压VREF = 10V,则最小分辨电压(LSB)为__mV。

分析设计题(共40分)

-

(10分) 化简逻辑函数

F(A,B,C,D) = Σm(0, 2, 5, 7, 8, 10, 13, 15),并用最少的与非门实现该函数。 -

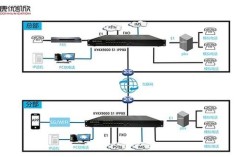

(15分) 分析下图所示时序逻辑电路的逻辑功能。(写出驱动方程、状态方程、状态表,并画出状态图)

(此处应有电路图,假设为:两个JK触发器FF0和FF1,时钟CLK连接到两个触发器的CLK端,J0=K0=Q1', J1=K1=Q0,假设无异步置位/复位端。)

-

(15分) 试用3线-8线译码器74LS138和必要的逻辑门,设计一个“不一致电路”,当三个输入变量A、B、C不相同时,输出F为1;否则F为0,请画出逻辑图。

综合应用题(共20分)

- (20分) 设计一个“110”序列检测器,该电路有一个输入端X和一个输出端Z,当连续输入三个或三个以上的‘1’之后,再输入一个‘0’时,输出Z为1,否则为0,要求:

- (1) 画出原始状态图。

- (2) 列出原始状态表。

- (3) 用状态化简方法(或观察法)得到最简状态图。

- (4) 若选用D触发器实现,请进行状态编码并求出驱动方程和输出方程。(假设状态分配:S0=00, S1=01, S2=10)

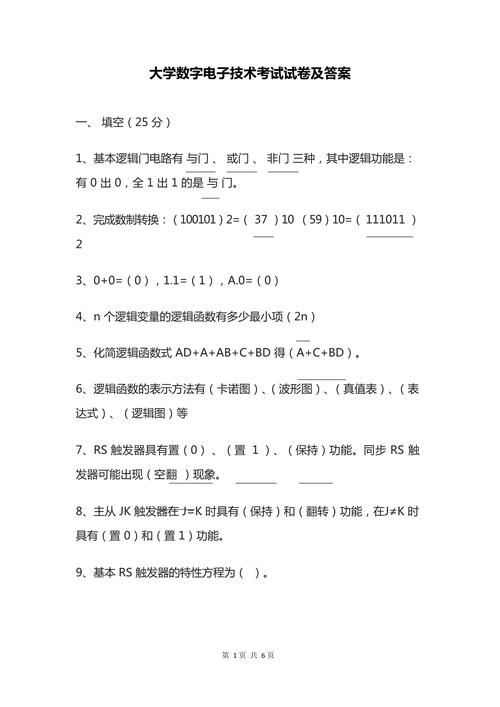

参考答案

选择题

- A (56 = 5×10 + 6 = 0101 0110)

- B (卡诺图化简,包围圈得到 C 和 AB)

- B (TTL门输入端接大电阻(>1kΩ)相当于接高电平)

- C (OC门的输出端可以直接并联实现“线与”)

- D (JK触发器的特性方程 Q = JQ' + K'Q,当J=K=1时,Q = Q')

- A (右移寄存器,先移入的位在最高位,输入

1011,4个脉冲后,1011被移入) - A (输出电压 Vout = -(VREF/2ⁿ) × D,其中D是十进制数。

10000000= 128,Vout = -(5/256) × 128 = -2.5V,题目问“约为”,且通常D/A转换器输出为单极性时,公式为 Vout = (VREF/2ⁿ) × D,结果为2.5V) - B (编码器的功能是将特定信号(如按键)转换为二进制代码)

- C

- C

填空题

- 或,非

- 八进制,十六进制

- 逻辑函数表达式,逻辑图

- 高阻态

- 1

- 2ⁿ, 2ⁿ - 1

- 输入状态,无关

- 存储电路(或触发器)

- 量化,编码

- 1/256 (或 1/2⁸), 39.0625 (10000mV / 256 ≈ 39.06mV)

分析设计题

- 解:

- 卡诺图化简:

CD AB 00 01 11 10 00 1 0 0 1 01 0 1 1 0 11 0 1 1 0 10

- 卡诺图化简: