什么是CoWoS技术?

CoWoS是一种先进的先进封装技术,它的核心思想是将多个独立的芯片(或裸片,Die)像拼图一样,高密度地集成在一个硅中介层上,然后再将这个整体封装到一个基板上。

这个长长的名字其实就描述了它的结构层次:

- Chip on Wafer (CoW):将多个“芯片”直接放置在一个“晶圆”上,这里的“晶圆”指的就是硅中介层。

- Wafer on Substrate (WoS):将集成了芯片的“晶圆”再安装到一个更大的“基板”上。

可以把它想象成盖房子:

- Chip (芯片):是预先在工厂里制造好的、功能各异的“预制件”(如承重墙、门窗、水电模块)。

- Wafer (中介层):是一块高精度的“地基/连接板”,上面有极其精密的布线,用于将这些“预制件”快速、准确地连接起来。

- Substrate (基板):是最终房子的“地基”,提供支撑和与外部世界(电源、信号)的连接。

CoWoS解决了什么问题?(为什么需要它?)

要理解CoWoS的价值,首先要明白它解决了什么核心痛点,这要从摩尔定律的放缓说起。

-

摩尔定律放缓,性能提升遇到瓶颈: 过去,芯片性能的提升主要依靠晶体管数量的增加(遵循摩尔定律),但随着工艺节点进入7纳米、5纳米甚至更先进,单纯缩小晶体管尺寸带来的性能提升和功耗下降越来越困难,且成本急剧上升。

(图片来源网络,侵删)

(图片来源网络,侵删) -

“More than Moore”趋势: 业界开始转向“超越摩尔定律”的思路,即通过封装技术来提升系统性能,将不同功能的芯片(如CPU、GPU、高带宽内存HBM)封装在一起,形成一个“芯粒”或“芯片系统”,是实现性能飞跃的关键。

-

传统封装的局限性: 传统的封装技术(如引线键合)连接的“引脚”数量有限(通常在几百到几千个),且信号传输距离长、速度慢、功耗高,无法满足AI芯片对超大数据带宽和低延迟的需求。

CoWoS的出现,就是为了解决这些问题:

- 超高带宽:通过中介层上成千上万个微小的凸块,芯片与HBM内存之间可以实现数千个连接,带宽比传统封装高出几十甚至上百倍。

- 极低延迟:芯片间的物理距离被大大缩短,信号传输路径变短,从而显著降低延迟。

- 高集成度:可以将逻辑芯片、I/O芯片和多个内存芯片(如HBM)封装在同一个模块内,实现系统级集成。

- 功耗优化:短距离的连接和优化的设计可以降低整体功耗。

CoWoS的结构和工作原理

一个典型的CoWoS封装结构如下(从下到上):

-

Substrate (基板):

- 作用:提供物理支撑,并作为与外部电路(如PCB板)的接口,它承载着整个CoWoS模块。

- 材料:通常是有机材料(如ABF基板)或硅基板。

-

Interposer (中介层):

- 这是CoWoS技术的核心!

- 作用:一个高密度布线的硅片,充当“交通枢纽”,它有数万甚至数十万个微小的铜凸块,用于连接下方的基板和上方的多个芯片。

- 优势:相比于在基板上直接布线,硅中介层可以实现更精细、更密集的布线,从而提供超高的I/O(输入/输出)密度。

-

Die(s) (裸片):

- 这是执行具体计算功能的芯片,在CoWoS中,通常会集成以下几种芯片:

- 逻辑芯片:如NVIDIA的GPU核心、AMD的CPU/GPU核心。

- HBM (高带宽内存):通常有2个、4个或8个HBM芯片堆叠在逻辑芯片周围。

- I/O芯片:负责处理与外部通信的信号。

- 这是执行具体计算功能的芯片,在CoWoS中,通常会集成以下几种芯片:

-

Underfill (底部填充胶):

- 在芯片和中介层之间填充的环氧树脂材料。

- 作用:增强机械强度,分散因热胀冷缩产生的应力,保护脆弱的凸块连接,提高产品的可靠性和寿命。

-

Redistribution Layer (RDL - 重布线层):

- 位于中介层顶部的额外金属层。

- 作用:由于中介层上的凸块位置是固定的,而芯片的I/O焊盘位置可能不匹配,RDL可以像“立交桥”一样,重新规划信号路径,将芯片的焊盘连接到中介层上对应的凸块上,提供了极大的设计灵活性。

CoWoS的主要类型

台积电的CoWoS技术也在不断演进,目前主要有以下几种类型:

| 类型 | 特点 | 主要应用 |

|---|---|---|

| CoWoS-S (Standard) | 标准版,使用硅中介层,HBM堆叠在逻辑芯片之上。 | AI GPU、高性能CPU,例如NVIDIA的H100、A100,AMD的Instinct MI300系列。 |

| CoWoS-R (Reduced) | 简化版/成本优化版,使用有机中介层(成本远低于硅中介层),去掉了部分RDL层,主要用于对成本敏感、带宽需求稍低的场合。 | 部分AI芯片、高性能网络芯片,例如NVIDIA的HGX H100平台。 |

| CoWoS-L (InFO_L) | 逻辑增强版,在CoWoS的基础上,进一步优化了逻辑芯片之间的连接,适用于需要多个高性能逻辑芯片集成的场景。 | CPU+GPU异构集成,例如苹果的M系列Ultra芯片。 |

| CoWoS-IC (InFO_oS) | 中介层上集成芯片,将I/O芯片也集成在中介层上,进一步缩短了逻辑芯片与I/O芯片的距离。 | 网络处理器、5G基带芯片等需要超高速数据通信的领域。 |

应用领域和市场影响

CoWoS技术是当前AI算力竞赛的“幕后英雄”。

-

人工智能/机器学习:

- 这是CoWoS最主要的应用领域,AI大模型训练需要巨大的计算能力和内存带宽,GPU通过CoWoS技术集成HBM,实现了“计算单元”和“存储单元”的超高频率数据交换,是训练像GPT这样的大模型的硬件基石。

-

高性能计算:

在科学计算、金融建模、气象预测等领域,需要处理海量数据,CoWoS提供的超高并行处理能力和带宽至关重要。

-

高性能网络/数据中心:

数据中心内部服务器之间、交换机之间需要超高速的数据交换,CoWoS技术被用于制造高速网络接口卡和交换芯片。

-

图形处理器:

顶级游戏GPU和专业图形卡也采用CoWoS技术,以获得更高的显存带宽,从而在4K/8K游戏和专业渲染中提供更流畅的体验。

市场影响:

- 台积电的“护城河”:CoWoS是台积电除先进制程外的另一大“杀手锏”,为其带来了丰厚的封装和测试收入,巩固了其在半导体产业链的领导地位。

- AI芯片的“入场券”:对于希望进入AI芯片市场的公司(如初创公司)能否获得台积电的CoWoS产能,直接决定了其产品的成败,CoWoS产能的争夺异常激烈,常常出现“一芯难求”的局面。

- 推动整个产业链发展:CoWoS的成功带动了上游材料(如硅中介层、ABF基板)、设备(如高精度贴片机)和下游设计(芯粒设计)的协同发展。

面临的挑战与未来展望

挑战:

- 成本高昂:硅中介层、精密设备和复杂的制造流程使得CoWoS封装成本极高,远超传统封装。

- 良率问题:集成度越高,工艺步骤越多,对准和良率的控制难度就越大,任何一个环节的瑕疵都可能导致整个模块报废。

- 散热问题:多个高性能芯片密集封装在一起,热量非常集中,如何有效散热是一个巨大的挑战。

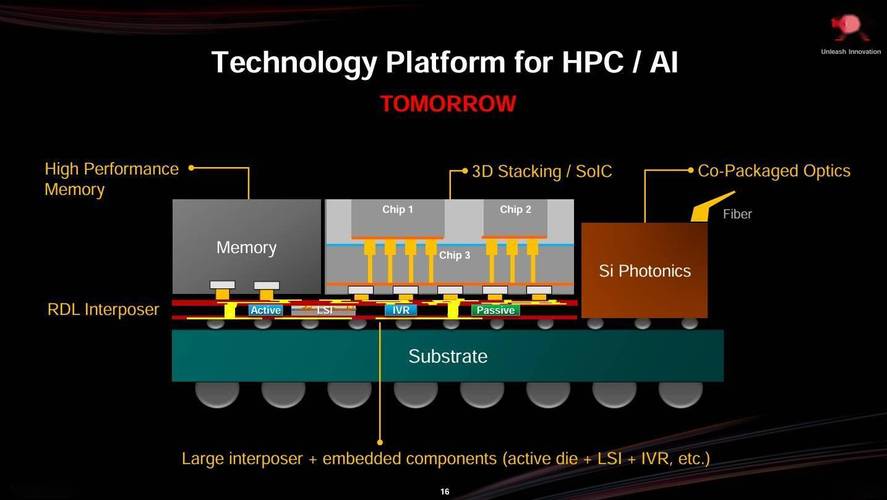

未来展望:

- 进一步集成和微缩:提高中介层的I/O密度,支持集成更多的芯粒。

- 3D堆叠技术:与InFO(Integrated Fan-Out)等技术结合,实现更立体、更紧凑的3D集成。

- 应对Chiplet(芯粒)浪潮:CoWoS是实现Chiplet设计的关键平台,未来将更好地支持不同工艺节点、不同功能的芯粒之间的异构集成。

- 成本优化:通过技术改进和规模化生产,努力降低CoWoS的成本,使其应用范围更广。

CoWoS技术是台积电在先进封装领域皇冠上的明珠,它通过创新的“中介层”架构,巧妙地绕过了先进制程的物理极限,通过系统级集成的方式,为AI、HPC等尖端应用提供了前所未有的算力、带宽和能效,它不仅是台积电巩固其技术领导地位的关键,更是驱动当前全球AI技术飞速发展的核心硬件引擎之一。