时钟数据恢复技术综述

摘要

时钟数据恢复是现代高速串行通信系统中的核心技术之一,它的主要任务是从接收到的、经过信道传输后发生畸变且不带时钟信息的串行数据流中,同时提取出原始的数据和与之同步的时钟信号,本文旨在对CDR技术进行系统性梳理,涵盖其基本原理、关键电路模块、主流实现方案、性能评估指标以及在不同领域的应用,并展望其未来的发展趋势。

引言:为什么需要CDR?

在早期的并行通信或低速串行通信中,发送端和接收端通常共享一条独立的时钟线路(如时钟-数据分离模式),但随着数据传输速率的不断提高,这种模式的弊端日益凸显:

- 成本与复杂性增加:需要额外的时钟线路和连接器,增加了硬件成本和布线复杂性。

- 时钟偏斜问题:时钟和数据信号在传输路径上可能存在不同的延迟,导致接收端采样时数据不稳定。

- 电磁干扰:额外的时钟线会引入更多的电磁干扰,影响信号完整性。

- 无法满足高速需求:在GHz级别的传输速率下,为时钟和数据提供完全匹配的物理路径变得异常困难。

为了解决这些问题,串行通信和源同步技术应运而生,发送端将时钟信息“嵌入”到数据流中,接收端则通过专门的电路——时钟数据恢复器——来从数据中“解码”出时钟和数据,CDR技术因此成为连接物理世界与数字世界的桥梁,是所有高速接口(如PCIe, SATA, Ethernet, DDR等)不可或缺的组成部分。

CDR的基本原理

CDR的核心工作原理是一个负反馈控制系统,其目标是使本地产生的时钟信号(VCO/压控振荡器的输出)的边沿精确地对准输入数据信号的过零点或最佳采样点,其基本流程如下:

- 数据输入:接收到的数据流通常是经过均衡、放大等预处理后的信号,但其边沿由于信道损耗、抖动和噪声的影响已经变得模糊。

- 相位检测:相位检测器比较输入数据和本地恢复时钟之间的相位差,并输出一个与相位误差成比例的电压或电流信号,这是整个系统的“眼睛”,负责判断时钟是“快了”还是“慢了”。

- 环路滤波:环路滤波器对相位检测器的输出进行低通滤波,它有两个关键作用:

- 平滑噪声:滤除相位检测器产生的高频噪声和抖动,防止系统不稳定。

- 决定动态特性:设置环路的带宽和阻尼系数,决定了CDR的跟踪速度(捕获范围)和抑制噪声的能力(抖动容限)。

- 时钟源:通常是压控振荡器,VCO的输出频率受环路滤波器输出的控制电压影响,当控制电压升高时,VCO频率升高;反之降低。

- 时钟输出与反馈:VCO产生的时钟信号被送回相位检测器,用于与下一个输入数据比特进行比较,同时也会作为最终的恢复时钟输出,用于数据寄存器的采样。

这个闭环系统会不断调整VCO的相位,直到其稳定在一个能够对输入数据进行最佳采样的状态。

CDR的关键电路模块

一个典型的CDR电路由以下几个关键模块构成:

-

相位检测器:

- 作用:检测数据与本地时钟的相位差。

- 常见类型:

- 鉴频鉴相器:常用于二电平数据,输出相位误差和方向信号。

- Hogge相位检测器:可以工作在任意数据模式(包括长连0或1),输出与相位误差成线性关系的电压信号,性能优越。

- Alexander相位检测器:结构更简单,但性能略逊于Hogge PFD。

-

环路滤波器:

- 作用:如前所述,是系统的“大脑”。

- 类型:通常是二阶或三阶的无源或有源RC滤波器,其参数(电阻、电容值)直接决定了环路的带宽和阻尼系数,需要在设计中仔细权衡。

-

压控振荡器:

(图片来源网络,侵删)

(图片来源网络,侵删)- 作用:产生本地时钟,是系统的“心脏”。

- 类型:

- LC-VCO:高频下相位噪声性能好,但集成度低,调谐范围窄。

- 环形振荡器:易于集成,调谐范围宽,但相位噪声性能相对较差,在大多数数字CDR设计中,环形振荡器是首选。

-

数据再生电路:

- 通常是一个由恢复时钟驱动的D触发器,它在恢复时钟的特定边沿(如上升沿)对输入数据进行采样,并输出最终恢复的干净数据。

主流CDR技术分类

根据实现架构和工作原理,CDR技术主要可分为以下几类:

1 基于锁相环的架构

这是最传统和经典的CDR架构,本质上是将PLL中的“相位比较器”替换为“相位检测器”,其参考输入从外部晶振变成了数据流本身。

-

线性/ bang-bang CDR:

- 工作原理:相位检测器输出非线性的“早/晚”或“+1/-1”信号,而不是连续的电压,环路滤波器后接电荷泵,将这种数字信号转换为对VCO的控制电压。

- 优点:结构简单,对数据模式不敏感,功耗低。

- 缺点:存在周期性抖动,环路带宽受限,动态性能稍差。

-

过采样/ Hogge CDR:

- 工作原理:采用Hogge相位检测器,输出与相位误差成线性关系的模拟电压信号,环路带宽可以设计得较宽,能够更好地跟踪数据变化。

- 优点:性能优越,抖动抑制能力强,眼图中心跟踪准确。

- 缺点:电路相对复杂,功耗较高。

2 基于边沿/过零点检测的架构

这类架构不依赖于数据比特的值,而是直接提取数据信号的边沿或过零点来重建时钟。

-

相位插值器 CDR:

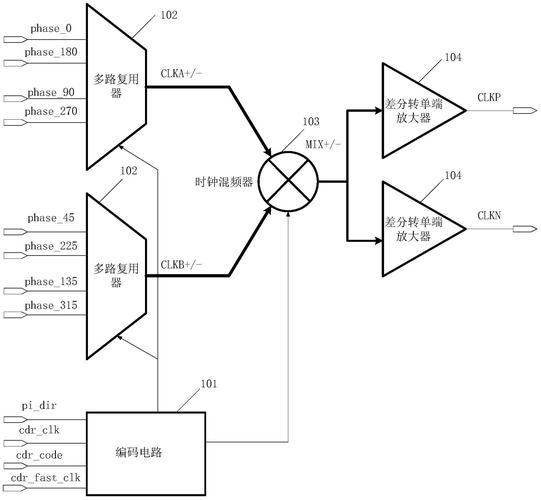

- 工作原理:使用一个高速、但相位精度不高的“多相时钟发生器”(通常由VCO和分频器实现),相位检测器判断当前数据眼图的最佳采样点位于哪个多相时钟之间,然后通过相位插值器 合成一个精确位于该点的时钟。

- 优点:非常适合高速应用(如28Gbps及以上),因为其核心部件(PI)可以工作在较低频率,易于实现,支持多相位(如4相位、8相位),灵活性高。

- 缺点:相位插值器的线性度和增益匹配是设计难点。

-

Swing CDR / 过零点检测:

- 工作原理:通过比较器检测数据信号的过零点,并利用这些过零点事件去控制一个振荡器,从而重建时钟,由于数据信号的边跳变(无论0到1还是1到0)都会产生过零点,因此它能有效克服长连0或1的问题。

- 优点:天然免疫于长连0/1数据模式。

- 缺点:对噪声非常敏感,因为噪声同样会产生虚假的过零点。

3 基于数字控制的架构

随着CMOS工艺进入深亚微米时代,数字电路的优越性(抗噪声、可移植性好、易于集成)使得全数字CDR成为研究热点。

-

数字锁相环 CDR:

- 工作原理:将传统PLL中的模拟模块(PFD, LF, VCO)全部用数字电路实现,用数字控制振荡器代替VCO,用数字滤波器代替LF。

- 优点:工艺可移植性强,不受工艺失配影响,便于通过软件算法优化性能,功耗和面积优势明显。

- 缺点:存在量化噪声,数字电路的“抖动”性能需要精心设计。

-

过采样 CDR:

- 工作原理:使用一个远高于数据速率的本地高速时钟对输入数据进行过采样,然后通过数字信号处理算法(如FIR滤波、维特比算法等)在过采样的数据点中寻找最佳的采样位置。

- 优点:性能非常灵活,可以通过算法优化来适应不同信道和抖动场景,精度高。

- 缺点:对处理器的计算能力和功耗要求极高,通常需要专用DSP。

CDR的关键性能指标

评估一个CDR的性能,主要关注以下几个指标:

- 抖动容限:CDR能够正常工作所能容忍的最大输入信号抖动,分为周期抖动容限和抖动转移函数。

- 抖动传递函数:描述输入抖动多大比例会“传递”到输出的恢复时钟上,JTF的带宽通常与CDR环路的带宽一致。

- 抖动生成:CDR自身电路(特别是VCO)引入的抖动,这是衡量CDR“纯净度”的关键指标。

- 捕获范围/锁定范围:CDR能够从失锁状态进入锁定状态的最大初始频率或相位偏差。

- 锁定时间:CDR从上电或大失锁状态到进入稳定锁定状态所需的时间。

- 误码率:在特定信噪比和抖动条件下,CDR输出数据的错误比特率,这是最终的、最严苛的衡量标准。

CDR技术的应用领域

CDR技术无处不在,是所有高速数据接口的基石:

- 有线通信:以太网(10G/25G/40G/100G/400G)、光纤通道、PCI Express、SATA、USB、HDMI。

- 无线通信:射频收发机中的时钟同步、基带处理。

- 存储系统:DDR内存接口、固态硬盘控制器。

- 光通信:光模块、相干光通信系统。

- 消费电子:高清视频传输、手机SoC内部及外部接口。

未来发展趋势

随着摩尔定律的延续和通信需求的爆炸式增长,CDR技术也面临着新的挑战和机遇:

- 更高集成度与SoC化:将CDR与其他收发机模块(如SerDes)集成在单芯片上,降低成本和功耗。

- 全数字与混合信号设计:数字CDR因其工艺无关性和可配置性,将在先进工艺节点(如7nm, 5nm)下占据主导地位,混合信号设计则试图在性能和灵活性之间取得平衡。

- 智能化与自适应CDR:引入机器学习或自适应算法,使CDR能够根据信道特性、抖动类型和线缆长度等动态调整自身参数(如环路带宽),实现最优性能。

- 面向新标准的支持:为PAM4、脉冲幅度调制等新型调制方式设计的CDR,需要更高的相位分辨率和更复杂的检测算法。

- 低功耗设计:在移动设备和物联网设备中,对功耗的要求极为苛刻,低功耗CDR设计是一个重要方向。

时钟数据恢复技术是连接物理信号世界与数字逻辑世界的桥梁,其重要性随着数据传输速率的提高而日益凸显,从最初的模拟PLL架构,到如今主流的相位插值器和全数字CDR,CDR技术不断演进,以适应更高速、更低功耗、更高集成度的应用需求,随着AI和先进工艺的发展,CDR将变得更加智能和高效,继续支撑着全球信息高速公路的畅通无阻,对于任何从事高速电路设计、通信系统研究的工程师而言,深入理解CDR原理和设计都是一项必备的核心技能。