eda技术与fpga在现代电子设计领域紧密相连,共同构成了数字系统开发的核心技术体系,eda(electronic design automation,电子设计自动化)技术是指利用计算机辅助工具完成电子系统设计、仿真、验证、测试等全流程的综合性技术,而fpga(field-programmable gate array,现场可编程门阵列)是一种半定制集成电路,通过硬件描述语言编程实现特定功能,两者的结合极大地提升了电子设计的灵活性和效率。

eda技术的发展历程与集成电路的复杂度提升密切相关,从早期的原理图设计工具,到如今支持系统级建模、验证和实现的完整平台,eda技术已覆盖从算法设计到物理实现的各个环节,在数字系统设计中,eda工具链通常包括设计输入、逻辑综合、功能仿真、时序分析、布局布线等模块,设计输入阶段可采用硬件描述语言(如vhdl、verilog)或高级建模语言(如systemc)进行系统描述;逻辑综合工具将高级行为描述转化为逻辑门级网表;功能仿真通过模拟输入输出验证设计逻辑的正确性;时序分析则检查电路在不同工艺、电压、温度条件下的时序是否满足要求;布局布线工具将网表映射到fpga的物理资源上,并优化布线延迟。

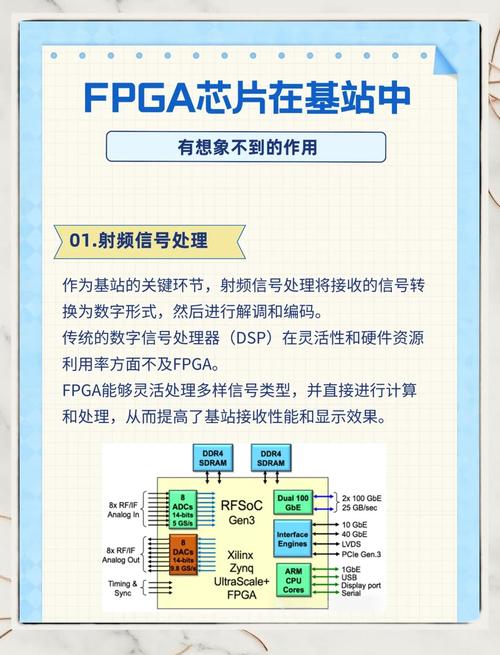

fpga作为一种可重构的硬件平台,其核心优势在于现场可编程性和并行处理能力,与asic(专用集成电路)相比,fpga无需流片即可修改设计,大幅降低了开发成本和风险;与dsp(数字信号处理器)等处理器相比,fpga通过硬件并行执行多个任务,在实时性和吞吐量方面具有显著优势,fpga的基本结构由可配置逻辑块(clb)、输入输出单元(io block)、块ram(bram)和数字时钟管理器(dcm)等组成,clb是实现逻辑功能的核心单元,通过查找表(lut)和触发器构成;io块负责芯片与外部信号的连接;bram提供片上存储资源;dcm用于时钟生成与分频,随着工艺进步,现代fpga还集成了dsp模块、高速收发器(如serdes)和硬核处理器系统(hps),使其能够处理更复杂的系统级任务。

eda技术与fpga的结合体现在设计流程的每个环节,在设计输入阶段,工程师可通过eda工具(如vivado、quartus)编写硬件描述代码,并利用图形化界面进行模块划分和信号连接,逻辑综合工具将代码转换为fpga厂商特定的网表格式,同时根据资源约束优化逻辑结构,功能仿真工具(如modelsim、iverilog)通过测试激励验证设计的功能正确性,避免后续阶段发现逻辑错误,时序分析工具(如prime time)通过静态时序分析(sta)检查关键路径的延迟,确保设计在目标fpga的工作频率下稳定运行,布局布线工具(如fitter)根据网表和约束条件,将逻辑映射到fpga的clb、bram等资源中,并优化布线长度和延迟,eda工具生成位流文件(bitstream),通过编程器下载到fpga中实现硬件功能。

以一个简单的数字滤波器设计为例,其eda与fpga开发流程如下:在matlab或systemc中完成算法建模和仿真,确定滤波器系数和结构;使用verilog或vhdl将算法描述为可综合的代码,并通过modelsim进行功能仿真;利用vivado进行逻辑综合,生成针对特定fpga(如xilinx artix-7)的网表;随后,通过vivado的布局布线工具优化资源使用,并进行时序分析;生成位流文件并下载到fpga中,通过逻辑分析仪或示波器验证滤波效果,整个流程中,eda工具提供了从算法到硬件的完整支持,而fpga则作为硬件载体实现了算法的并行化执行。

为了更清晰地展示eda工具在fpga设计各阶段的作用,以下表格总结了常用eda工具及其功能:

| 设计阶段 | 常用eda工具 | 主要功能 |

|---|---|---|

| 设计输入 | Vivado、Quartus II | 支持vhdl/verilog编写、原理图输入、ip核集成 |

| 逻辑综合 | Synplify Pro | 将hdl代码转换为逻辑门级网表,优化面积和时序 |

| 功能仿真 | ModelSim、Questa | 验证设计逻辑功能,通过测试激励检查输出结果 |

| 时序分析 | PrimeTime | 静态时序分析,检查建立时间、保持时间等时序约束 |

| 布局布线 | Vivado Fitter | 将网表映射到fpga资源,优化布线延迟和资源利用率 |

| 位流生成与下载 | iMPACT、JTAG | 生成位流文件,通过jtag或spi接口下载到fpga |

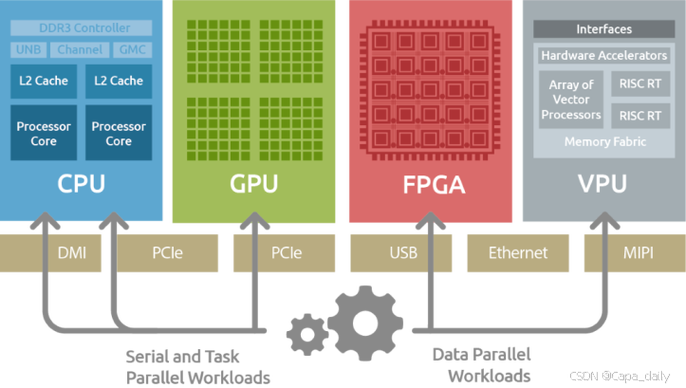

eda技术与fpga的发展趋势也呈现出深度融合的特点,eda工具正向智能化和云化方向发展,通过机器学习优化布局布线算法,利用云计算平台提供大规模并行仿真;fpga向更高集成度、更低功耗和更强计算能力演进,如集成ai加速模块的fpga(xilinx versal、intel stratix 10)可支持深度学习推理任务,基于fpga的异构计算平台,结合cpu、gpu和fpga的优势,已成为数据中心、5g通信、自动驾驶等领域的关键技术。

eda与fpga的结合仍面临挑战,复杂系统的验证成本高昂,需要更高效的仿真方法和形式化验证工具;fpga的功耗优化问题随着工艺节点缩小日益突出,需要eda工具提供更精确的功耗模型;硬件设计的高门槛也推动了高级综合(hls)工具的发展,允许工程师使用c/c++等语言直接描述硬件功能,降低设计难度。

相关问答FAQs:

Q1: eda技术与fpga在电子设计中的具体关系是什么?

A1: eda技术是电子设计的自动化工具链,涵盖了从算法建模、逻辑设计到物理实现的全流程;fpga则是eda工具的硬件载体,通过可编程逻辑实现特定功能,eda工具负责将设计意图转化为fpga可执行的配置文件(如位流),而fpga通过硬件并行执行实现高性能计算,两者相辅相成,eda提升了fpga设计的效率,fpga则扩展了eda技术的应用场景。

Q2: 为什么现代fpga设计越来越依赖eda工具?

A2: 现代fpga的集成度和复杂度大幅提升,单颗fpga可包含数千万至数十亿逻辑门,手动设计已无法满足需求,eda工具通过自动化流程(如逻辑综合、布局布线、时序分析)大幅减少人工干预,确保设计的正确性和高效性,eda工具支持ip核复用、多语言设计和跨平台仿真,进一步缩短了开发周期,降低了设计风险,因此成为现代fpga设计的必备工具。