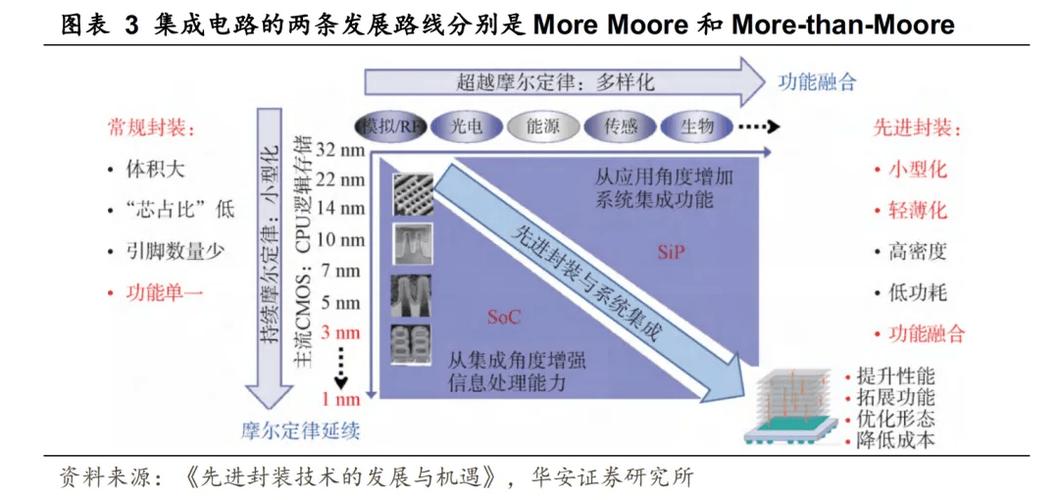

微电子封装技术作为半导体产业链中的关键环节,其发展历程见证了电子设备从大型化到小型化、从单一功能到系统集化的跨越,随着摩尔定律持续推进,芯片特征尺寸不断缩小,封装技术已从早期的“保护管壳”演变为实现系统级集成的核心载体,在提升芯片性能、降低功耗、增强可靠性等方面发挥着不可替代的作用。

微电子封装技术的发展历程

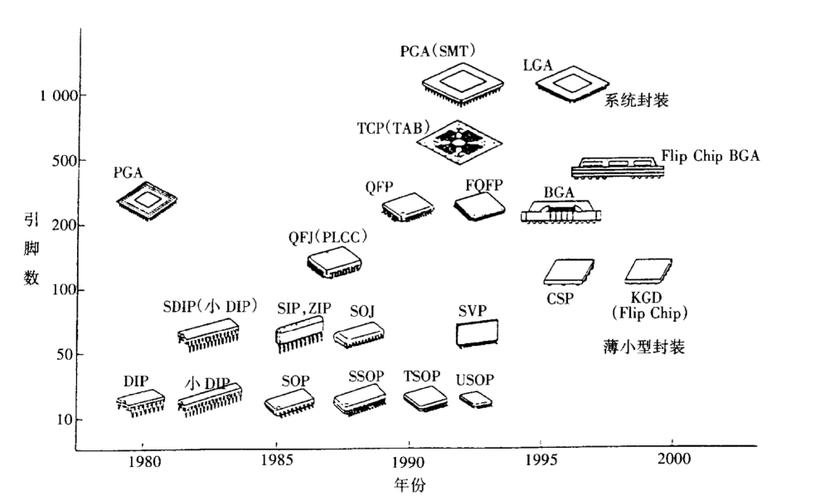

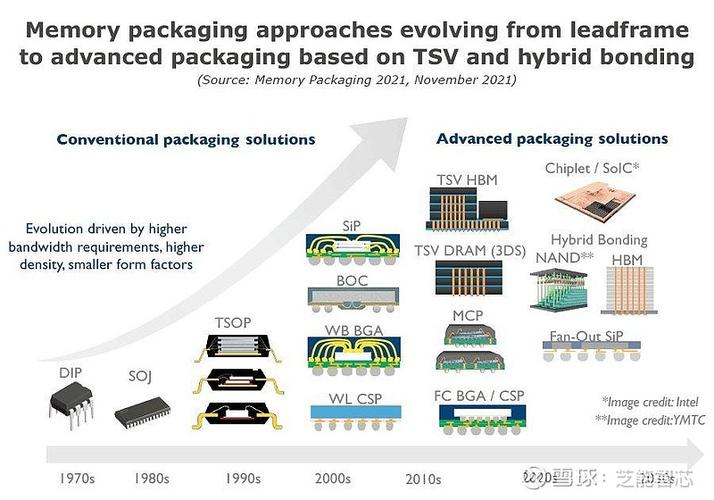

微电子封装技术的发展与芯片制造工艺、应用需求紧密相关,大致可分为四个阶段:

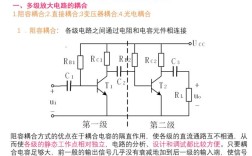

初期阶段(20世纪50-60年代):通孔插装技术

这一时期以晶体管和中小规模集成电路(SSI/MSI)为代表,封装形式以金属圆形封装(TO型)和双列直插封装(DIP)为主,DIP通过引脚插入PCB板孔实现电气连接,工艺简单、成本低,但封装密度低,引脚数量有限(通常低于64个),无法满足高性能计算需求,此阶段封装的核心功能仅为机械保护和电气连接,对性能提升的贡献有限。

高密度发展阶段(20世纪70-90年代):表面贴装技术

随着集成电路进入大规模(LSI)和超大规模(VLSI)时代,DIP的插装方式难以适应高密度组装需求,表面贴装技术(SMT)应运而生,引脚设计演变为翼形或J形,直接贴装在PCB表面,这一阶段出现了塑料四边引脚扁平封装(PQFP)、球栅阵列封装(BGA)等新型封装,BGA用焊球替代引脚,实现了引脚间距缩小(如1.0mm、0.8mm)和数量提升(可达数百个),显著提高了封装密度和散热性能,成为计算机CPU、显卡等高性能芯片的主流封装方案。

系统级封装阶段(21世纪初-2010年代):异构集成与多功能融合

摩尔定律逼近物理极限后,单纯依靠芯片尺寸缩小的路径逐渐受阻,系统级封装(SiP)技术成为突破方向,SiP将不同工艺、不同功能的芯片(如处理器、存储器、传感器等)封装在同一基板上,通过高密度互连实现系统级功能,这一阶段的关键技术包括:

- 芯片尺寸封装(CSP):封装尺寸接近芯片本身,适用于移动设备等小型化场景;

- 晶圆级封装(WLP):在晶圆级完成封装工艺,减少切割后的封装步骤,提升生产效率;

- 硅通孔(TSV):在芯片内部垂直钻孔,实现层间直接互连,极大缩短信号传输路径,提升3D集成能力。

智能手机中的射频模组、传感器模组均采用SiP技术,实现了高度集成和小型化。

先进封装阶段(2010年代至今):超越摩尔定律的协同创新

当前,先进封装已成为延续摩尔定律的核心驱动力,技术特征向“超多引脚、超高密度、超高频高速、超低功耗”发展,代表性技术包括:

- 5D/3D封装:通过硅中介层(Interposer)或TSV将多层芯片堆叠,如英特尔的Foveros技术实现了芯片的3D堆叠,大幅提升计算密度;

- 扇出型封装(Fan-Out):将芯片引脚重新分布并封装在塑封体外部,适用于高频通信芯片(如5G射频前端);

- Chiplet(芯粒)技术:将复杂芯片拆分为多个功能芯粒,通过先进封装集成,降低设计成本,提升良率,AMD的Ryzen处理器采用Chiplet技术,将CPU核心与I/O模块封装,实现了性能与成本的平衡。

微电子封装技术的关键演进方向

微电子封装技术的发展围绕“性能提升、尺寸缩小、成本降低”三大目标,具体体现在以下维度:

| 技术维度 | 早期技术 | 当前先进技术 | 核心优势 |

|---|---|---|---|

| 互连技术 | 引脚插装(DIP) | 焊球阵列(BGA)、TSV | 互连密度提升10倍以上,信号延迟降低 |

| 散热管理 | 金属基座散热 | 微流控散热、金刚石基板 | 功耗密度提升5倍,温度控制精度达±1℃ |

| 材料应用 | 环氧树脂塑封 | 低介电常数材料、纳米银烧结 | 信号损耗降低30%,散热效率提升50% |

| 集成度 | 单芯片封装 | 3D集成、SiP、Chiplet | 系统集成度提升100倍,体积缩小60% |

面临的挑战与未来趋势

尽管微电子封装技术取得了显著进展,但仍面临诸多挑战:一是3D堆叠中的热管理难题,高功率芯片堆叠易导致热点集中;二是异质材料间的热膨胀系数(CTE)失配,可能引发封装分层或失效;三是先进封装的制造成本较高,限制了部分领域的应用。

微电子封装技术将向“智能化、柔性化、绿色化”方向发展:

- 智能化封装:通过集成传感器实时监测芯片温度、应力等参数,实现自适应调控;

- 柔性封装:采用柔性基板和可拉伸互连技术,满足可穿戴设备、柔性显示等新兴需求;

- 绿色封装:开发无铅、无卤环保材料,以及低能耗封装工艺,响应碳中和目标。

相关问答FAQs

Q1:什么是Chiplet技术,它与传统封装有何区别?

A:Chiplet(芯粒)技术是将复杂功能芯片拆分为多个具有特定功能的小型芯片(芯粒),通过先进封装(如2.5D/3D集成)实现系统级集成的方案,与传统单芯片封装相比,Chiplet的优势在于:①降低设计复杂度和成本,芯粒可复用成熟工艺,避免全芯片采用先进制程的高风险;②提升良率,单个芯粒缺陷不影响整个系统;③灵活扩展,可根据需求组合不同芯粒,实现定制化功能,通过将CPU、GPU、内存芯粒封装,可高效构建高性能计算系统。

Q2:先进封装如何解决摩尔定律放缓带来的瓶颈问题?

A:摩尔定律放缓主要源于芯片制程逼近物理极限,研发成本和难度指数级增长,先进封装通过“超越摩尔”路径提供解决方案:①通过3D堆叠、SiP等技术提升单位面积集成度,弥补制程缩小的瓶颈;②Chiplet实现“异构集成”,将不同工艺的芯粒(如7nm CPU+28nm I/O)封装,兼顾性能与成本;③TSV、硅中介层等缩短互连长度,降低信号延迟和功耗,提升芯片运行效率,本质上,先进封装从“系统级优化”延续摩尔定律,成为后摩尔时代的核心驱动力。