EDA技术与应用重点

EDA(Electronic Design Automation,电子设计自动化)技术是现代集成电路设计与电子系统开发的核心支撑工具,它以计算机为平台,融合了图形学、拓扑逻辑学、微电子工艺、计算数学等多学科知识,实现了电子设计从物理级描述到系统级验证的全流程自动化,随着集成电路工艺节点不断突破7nm、5nm甚至3nm,EDA技术已成为推动半导体产业发展的关键引擎,其应用重点涵盖了设计、仿真、验证、测试等全生命周期,深刻影响着芯片的性能、成本与上市时间。

EDA技术的核心在于通过标准化工具链解决复杂电子系统的设计难题,在数字电路设计领域,重点包括RTL(Register Transfer Level)代码编写与逻辑综合,工程师使用Verilog或VHDL等硬件描述语言进行功能建模,通过EDA工具将其转换为门级网表,并结合工艺库信息进行逻辑优化、时序分析与功耗分析,这一过程中,时序收敛是关键挑战,需借助静态时序分析(STA)工具检查电路在不同工艺、电压、温度(PVT)条件下的时序余量,确保设计满足时钟频率要求,对于模拟/混合信号电路,EDA工具则侧重于SPICE仿真、版图设计与参数提取,需精确模拟器件的物理特性,如寄生电容、电阻等,以保证电路的精度与稳定性。

在系统级设计阶段,EDA技术的应用重点转向高层次综合(HLS)与虚拟原型验证,HLS工具允许工程师使用C/C++或SystemC等高级语言描述算法,自动生成RTL代码,大幅缩短复杂算法(如AI加速器、通信基带)的设计周期,虚拟原型则通过构建可执行的系统模型,在早期硬件开发阶段验证软件与硬件的协同工作,避免后期设计返工,多物理场仿真也是系统级设计的重要环节,例如通过电磁场仿真分析高速信号线的串扰问题,或通过热仿真评估芯片的散热设计,确保系统的可靠性。

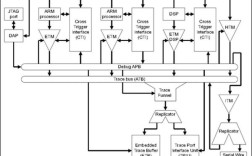

随着芯片集成度提升,EDA技术在验证环节的应用重点转向形式化验证与硬件仿真加速,形式化验证通过数学方法证明设计满足规范要求,相比传统仿真覆盖更全面的场景,尤其适用于协议验证、安全性关键模块的验证,硬件仿真器(如FPGA原型验证系统)则通过将设计映射到FPGA阵列,实现比软件仿真快3-5个数量级的运行速度,用于大规模SoC的功能验证,机器学习技术正逐步融入EDA工具,例如通过训练神经网络预测时序违例、优化布局布线,或自动修复设计缺陷,提升设计效率。

在制造环节,EDA技术的应用重点包括可制造性设计(DFM)与测试性设计(DFT),DFM通过在设计中引入规则检查(如天线效应、密度均匀性),确保设计能够稳定地通过光刻、刻蚀等工艺步骤;而DFT则通过扫描链、内建自测试(BIST)等技术,提升芯片的可测试性,降低测试成本,对于先进封装技术(如2.5D/3D IC),EDA工具还需解决异构集成中的信号完整性、电源完整性问题,确保多芯片协同工作的稳定性。

EDA技术的应用重点还体现在跨领域协同与标准化,现代电子设计往往涉及多个团队与工具链,因此需要支持IP复用、接口标准化(如UVM验证方法学)的协作平台,随着汽车电子、物联网等新兴领域的发展,低功耗设计、功能安全(ISO 26262)等也成为EDA工具的重要优化方向,例如通过电源门控技术降低待机功耗,或通过冗余设计满足ASIL等级安全要求。

| 应用领域 | 核心技术重点 | 典型工具/方法 |

|---|---|---|

| 数字电路设计 | RTL综合、时序分析、功耗优化 | Synopsys DC, Cadence Innovus |

| 模拟/混合信号设计 | SPICE仿真、版图设计、参数提取 | Cadence Virtuoso, Synopsys HSPICE |

| 系统级设计 | 高层次综合、虚拟原型、多物理场仿真 | Xilinx Vitis HLS, Ansys HFSS |

| 验证 | 形式化验证、硬件仿真加速、UVM方法学 | Cadence JasperGold, Siemens Polaris |

| 制造与测试 | DFM、DFT、良率提升 | Mentor Calibre, Synopsys TestMax |

| 新兴领域 | 低功耗设计、功能安全、异构集成 | Cadence Joules, Cadence Integrity |

相关问答FAQs:

Q1:EDA工具在5nm及以下先进工艺节点面临哪些主要挑战?

A1:在5nm及以下工艺节点,EDA工具面临多重挑战:一是量子效应与短沟道效应加剧,需引入更精确的器件模型(如FinFET、GAA晶体管模型);二是寄生效应(如电阻、电容)对电路性能的影响显著增强,需采用三维电磁场仿真与寄生参数提取技术;三是光刻工艺复杂性提升(如多重曝光、EUV光刻),需增强DFM规则以解决掩码版修正、套刻误差等问题;四是设计规模与验证复杂度指数级增长,需结合AI技术实现智能优化与验证加速。

Q2:如何理解EDA技术中的“跨层次协同设计”?

A2:跨层次协同设计指在电子系统开发中,实现从系统级、算法级、RTL级到门级、晶体管级的全流程无缝衔接,其核心在于通过统一的建模语言(如SystemC)与数据格式(如IP-XACT),确保不同层次设计的一致性,在AI芯片设计中,算法工程师使用Python描述神经网络模型,通过HLS工具转换为RTL代码,验证工程师再基于UVM方法学搭建验证平台,最终通过物理设计工具实现布局布线,跨层次协同可减少设计迭代次数,缩短开发周期,是应对复杂系统设计的关键方法。