CMOS芯片设计技术是现代集成电路设计的核心,它基于互补金属氧化物半导体(CMOS)工艺,通过PMOS和NMOS晶体管的组合实现逻辑功能,具有低功耗、高集成度和抗干扰能力强等优势,随着半导体工艺进入纳米时代,CMOS设计技术不断演进,涵盖了从架构设计到物理实现的完整流程,并面临诸多挑战与创新需求。

CMOS芯片设计技术始于20世纪60年代,随着摩尔定律的驱动,晶体管特征尺寸不断缩小,从微米级迈向纳米级,主流工艺节点已达到7nm、5nm甚至3nm,每代工艺的提升都带来晶体管密度和性能的飞跃,但也伴随着设计复杂度、功耗和成本的急剧增加,CMOS技术的核心优势在于其静态功耗极低(仅在状态切换时消耗功耗),且通过阈值电压调节、多阈值电压(MVT)技术等手段,可进一步优化动态与静态功耗的平衡。

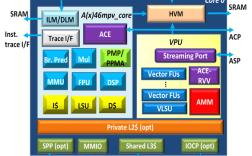

在架构设计阶段,CMOS芯片采用自顶向下的设计方法,首先定义系统级功能规格,如处理器、存储器或专用集成电路(ASIC)的应用场景,现代CMOS设计高度依赖硬件描述语言(HDL)如Verilog和VHDL,通过逻辑综合将行为级描述转换为门级网表,这一阶段需考虑并行处理、流水线架构、缓存层次等设计模式,以提升芯片性能,在CPU设计中,超标量架构和乱序执行技术通过增加指令级并行性(ILP)提高吞吐量,而神经网络处理器(NPU)则通过脉动阵列(Systolic Array)优化矩阵运算效率。

逻辑设计阶段将架构转化为逻辑电路,采用标准单元库(包含与门、或门、触发器等预设计模块)进行逻辑综合,关键挑战包括时序闭合(Timing Closure)和功耗优化,时序分析需确保信号在时钟周期内正确传输,避免建立时间(Setup Time)和保持时间(Hold Time)违规,静态时序分析(STA)工具通过计算最大/最小延迟路径来验证时序,而物理设计阶段的布局布线(Placement & Routing)会进一步影响时序,因此需迭代优化,功耗方面,动态功耗主要由开关电容引起(公式为P=αCV²f,为开关活动因子),可通过动态电压频率调节(DVFS)、门控时钟(Clock Gating)等技术降低;静态功耗则由漏电流导致,采用高k金属栅(HKMG)工艺和体偏置(Body Biasing)技术可缓解。

物理设计是将逻辑网表转化为实际版图的过程,包括布局(Placement)、布线(Routing)、时钟树综合(Clock Tree Synthesis, CTS)和验证(Verification),布局阶段需将标准单元合理排列,同时考虑功耗、时序和信号完整性;布线则完成金属互连,通常分为全局布线(Global Routing)和详细布线(Detailed Routing),随着工艺节点缩小,互连延迟成为性能瓶颈,需采用多层金属和低k介质材料降低RC延迟,时钟树综合通过插入缓冲器(Buffer)平衡时钟 skew,确保所有触发器同时接收时钟信号,物理验证包括设计规则检查(DRC)、布局与原理图一致性检查(LVS)和寄生参数提取(PEX),确保版图符合工艺要求并匹配逻辑设计。

随着工艺进入FinFET和GAA(Gate-All-Around)晶体管时代,CMOS设计面临新的挑战,FinFET通过三维栅极结构控制短沟道效应,但引入了复杂的三维建模和工艺变异问题;EUV(极紫外光刻)技术的应用提高了制程精度,但也增加了掩膜成本,芯片设计需应对IR Drop(电压降)和EM(电子迁移)效应,通过电源网络分析和冗余设计保障可靠性,在先进节点,芯粒(Chiplet)技术成为趋势,将不同功能的小芯片通过2.5D/3D封装集成,降低设计复杂度和成本,同时提升良率。

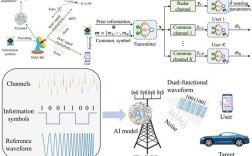

CMOS设计工具链也不断演进,EDA(电子设计自动化)工具如Synopsys的DC(Design Compiler)、PT(PrimeTime)和Cadence的Innovus成为主流,支持AI辅助设计,通过机器学习优化布局布线,验证环节采用形式验证(Formal Verification)和仿真加速技术(如FPGA原型验证),缩短验证周期。

CMOS技术将向更小节点(如2nm、1nm)演进,探索新材料(如二维材料碳纳米管)和新器件结构(如垂直晶体管),同时结合存算一体(In-Memory Computing)等架构突破传统冯·诺依曼瓶颈,量子计算与CMOS的融合、可重构计算(Reconfigurable Computing)也将成为研究方向。

相关问答FAQs

-

问:CMOS芯片设计中的“功耗-性能-面积”(PPA)如何平衡?

答:PPA平衡是CMOS设计的核心挑战,性能优化通常需要增加晶体管数量(提升面积)或提高工作频率(增加动态功耗);功耗优化则可能通过降低电压或频率牺牲性能,实际设计中,需根据应用场景优先级调整:对高性能计算(如GPU),优先保证性能,采用多电压域和动态频率调节;对低功耗场景(如IoT芯片),则侧重降低功耗,通过门控电源和异步设计减少能耗,EDA工具提供PPA分析脚本,支持在不同约束下探索最优解。 -

问:先进工艺节点(如3nm及以下)给CMOS设计带来哪些主要挑战?

答:先进节点的主要挑战包括:①工艺变异加剧,导致晶体管阈值电压和驱动电流不一致,需引入统计静态时序分析(SSTA)和自适应电路设计;②互连延迟占比提升,需采用RDL(重分布层)和光刻偏移技术优化布线;③制造成本飙升,EUV光刻和多重曝光增加流片费用,推动芯粒和设计复用;④量子效应显著,需考虑隧穿电流和热噪声,采用新型器件结构(如GAA FET)替代传统FinFET,设计周期延长也推动AI辅助设计工具的应用,以提升效率。