PCIe总线技术平台作为现代计算机系统中的核心互连技术,其发展历程、技术架构和应用场景深刻影响着计算、存储、网络等多个领域,自2003年Intel推出PCIe 1.0标准以来,该技术经历了多次迭代升级,从最初的2.5GT/s传输速率发展到如今的PCIe 6.0的64GT/s,带宽提升超过25倍,已成为连接CPU、GPU、SSD、网卡等关键硬件设备的高速通道,本文将从技术原理、架构演进、关键特性及典型应用四个维度,系统解析PCIe总线技术平台的内核逻辑与发展趋势。

PCIe总线的技术原理与架构基础

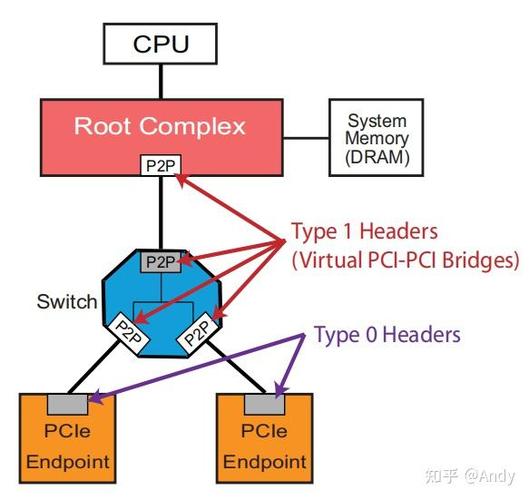

PCIe(Peripheral Component Interconnect Express)采用基于交换机的串行点对点拓扑结构,取代了传统PCI总线的共享并行总线架构,从根本上解决了带宽瓶颈和信号干扰问题,其物理层通过差分信号传输(TX/RX)实现数据交互,基本数据传输单元为“数据包”,包含地址包、数据包和完成包三种类型,每个PCIe链路由1条或多条通道(Lane)组成,每条通道支持双向传输,PCIe 1.0每条单通道带宽为250MB/s,后续版本通过提升编码效率(如PCIe 3.0采用128b/130b编码)和传输速率(如PCIe 6.0采用PAM4调制)实现带宽倍增。

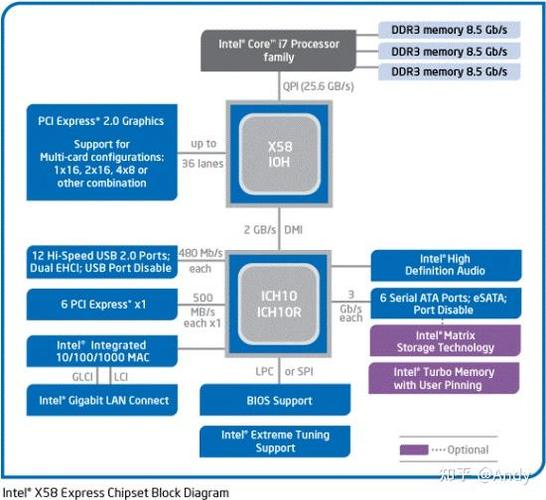

从架构层级看,PCIe采用分层设计:物理层(PHY)负责电气信号转换,数据链路层(Data Link)确保数据可靠传输(通过ACK/NAK机制实现错误重传),事务层(Transaction)处理TLP(事务层包)的路由与解析,典型系统中,CPU通过PCIe根复合体(Root Complex)连接设备,而交换机(Switch)则负责扩展多设备连接,形成树状拓扑结构,高端服务器中,单个PCIe 5.0交换机可支持多达64个通道,提供高达64GB/s的聚合带宽,满足大规模并行计算需求。

技术迭代与性能演进

PCIe标准的迭代遵循“每3-4年一代”的规律,关键性能指标呈指数级增长,下表对比了各主要版本的参数差异:

| 版本 | 发布年份 | 单通道带宽(GT/s) | 编码方式 | 每x16带宽(GB/s) | 典型应用场景 |

|---|---|---|---|---|---|

| PCIe 1.0 | 2003 | 5 | 8b/10b | 0 | 传统外设、早期SSD |

| PCIe 2.0 | 2007 | 0 | 8b/10b | 0 | 高速网卡、入门级GPU |

| PCIe 3.0 | 2010 | 0 | 128b/130b | 0 | 数据中心SSD、中端GPU |

| PCIe 4.0 | 2025 | 0 | 128b/130b | 0 | 高性能计算、AI加速卡 |

| PCIe 5.0 | 2025 | 0 | 128b/130b | 0 | 服务器存储、5G基站 |

| PCIe 6.0 | 2025 | 0 | PAM4 | 0 | 超算集群、高性能网络 |

值得注意的是,PCIe 6.0首次引入PAM4四电平调制技术,使单通道传输速率翻倍的同时,功耗效率提升约30%,为AI训练、实时数据分析等场景提供了硬件基础,而即将推出的PCIe 7.0(预计2025年)目标速率达128GT/s,将进一步推动CXL(Compute Express Link)等互连标准的融合,实现CPU、内存与I/O设备的一致性内存访问。

关键特性与技术优势

PCIe总线技术平台的核心优势体现在高带宽、低延迟、可扩展性和兼容性四个维度,在带宽方面,PCIe 6.0的x16通道已达到64GB/s,足以支持8K视频流处理或4块企业级NVMe SSD的并行读写;延迟方面,PCIe 3.0的端到端延迟控制在100ns以内,PCIe 5.0进一步优化至50ns以下,满足实时计算需求,可扩展性上,通过PCIe桥接芯片和交换机,系统可支持数百个设备级联,如分布式存储系统中单节点可连接32个NVMe SSD。

PCIe引入的“热插拔”(Hot-Plug)和“电源管理”(ASPML)特性,使得服务器和存储设备可在不停机的情况下维护硬件,大幅提升系统可用性,在安全层面,PCIe 4.0新增的“链路层加密”(Link-layer Encryption)功能,有效防止数据篡改和窃听,适用于金融、医疗等高安全场景。

典型应用场景

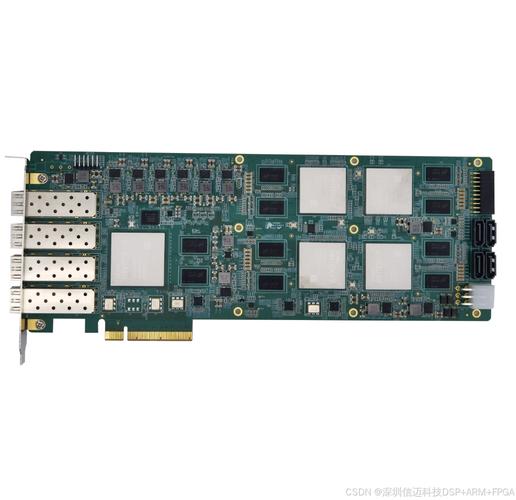

PCIe总线技术平台的应用已从传统PC扩展到云计算、人工智能、边缘计算等前沿领域,在数据中心,PCIe 5.0 NVMe SSD(如Samsung 990 PRO)通过4通道实现14GB/s顺序读写,支撑数据库和虚拟化平台的高并发访问;AI领域,NVIDIA A100/H100 GPU采用PCIe 4.0/5.0接口,与CPU直接互联,带宽达600GB/s以上,加速大模型训练;边缘计算中,PCIe 3.0加速卡(如Intel FPGA)实现实时视频处理和协议转换,满足工业物联网的低延迟需求。

相关问答FAQs

Q1: PCIe总线与传统的PCI总线有哪些本质区别?

A1: PCIe与PCI的核心区别在于拓扑结构和传输方式:PCI采用共享并行总线,所有设备竞争带宽,易形成性能瓶颈;而PCIe采用串行点对点连接,每条设备独享通道带宽,支持全双工传输,PCIe支持热插拔、更高带宽(PCI 32bit/33MHz带宽仅133MB/s,PCIe 4.0 x16达16GB/s)和更低的信号干扰,适合现代高性能设备需求。

Q2: 为什么PCIe 6.0需要采用PAM4调制技术?

A2: PCIe 6.0目标是将速率从PCIe 5.0的32GT/s提升至64GT/s,若继续沿用NRZ(二进制)调制技术,信号频率需翻倍至64GHz,这将导致信号衰减急剧增加、功耗大幅上升,且现有PCB板材和连接器难以支持,PAM4通过每符号传输2比特(4种电平),在相同波特率下实现带宽倍增,同时将信号频率控制在32GHz,兼顾性能与信号完整性,是当前高速互连技术的必然选择。