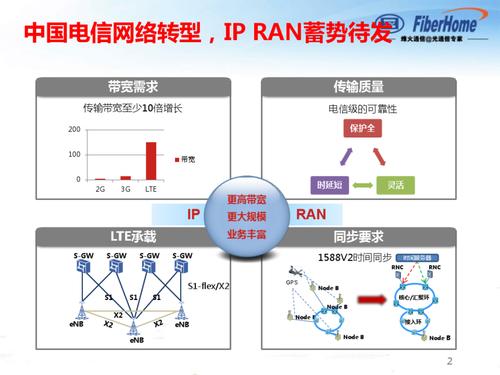

IP RAN(IP Radio Access Network)技术是移动承载网络的核心架构,主要用于4G/5G基站回传及固定宽带接入,其技术参数直接决定了网络的性能、可靠性和扩展性,以下从关键维度详细解析IP RAN的核心技术参数。

网络分层与架构参数

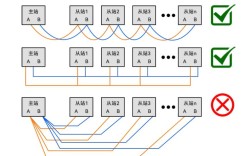

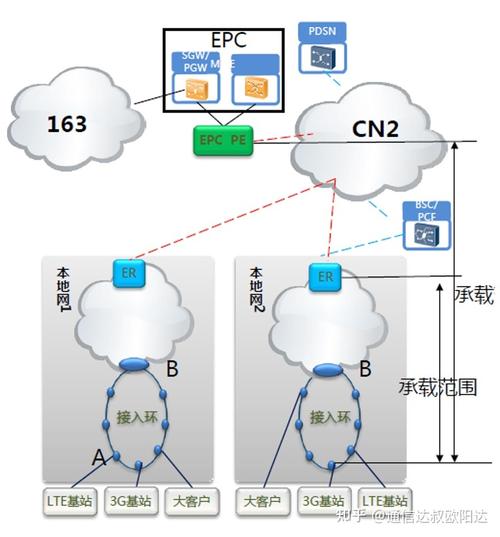

IP RAN通常采用分层架构,包括核心层、汇聚层和接入层,各层参数需协同设计,核心层聚焦高速转发和路由策略,典型设备为高端路由器,支持100G/400G端口,转发性能≥10Tbps;汇聚层负责流量聚合与QoS调度,设备需支持50G/100G端口,转发能力≥1Tbps;接入层直接连接基站,采用多业务接入设备(如PTN/IPRAN接入盒),端口密度≥24×GE/10×10GE,支持同步以太网(SyncE)和1588v2精密时间同步,时间同步精度≤1.5μs(5G场景要求≤500ns),架构上需支持环形、链形、Mesh组网,环网保护倒换时间≤50ms(ITU-T G.813标准)。

性能参数

- 转发性能:接入层设备整机转发率≥20Mbps,汇聚层≥100Mbps,核心层≥10Tbps;包转发率≥36Mpps(千兆端口),需支持64字节小包线速转发,避免基站流量拥塞。

- QoS能力:支持8级队列调度(如PQ+WRR)、流量监管(CAR)和整形(CBS),确保语音(VoLTE)、视频等高优先级业务时延≤20ms,抖动≤1ms;需支持DiffServ模型,实现DSCP优先级映射,基站业务隔离度≥40dB。

- 带宽与扩展性:单端口支持10GE/25GE/100GE,未来平滑升级至400G;带宽利用率≤70%(峰值),保障突发流量处理能力,支持FlexE(灵活以太网)切片,单切片带宽≥100Mbps。

可靠性参数

- 保护机制:环网保护(如RPR、MPLS-TP)倒换时间≤50ms,设备级支持1+1热备份、VRRP(虚拟路由冗余协议),主控板和电源板均需冗余,MTBF(平均无故障时间)≥10万小时。

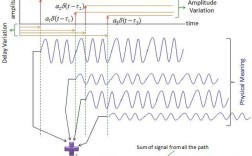

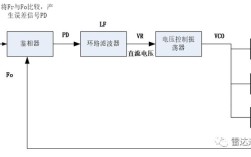

- 同步性能:支持IEEE 1588v2(PTPv2)和SyncE,主从时钟精度≤±20ppb(1588v2),时间戳分辨率≤8ns,满足5G基站同步需求;支持SSM(同步源选择)协议,防止时钟环路。

- 生存性:支持链路聚合(LACP,最多8条链路聚合)、快速重路由(FRR),业务中断时间<10ms;设备支持-40℃~70℃宽温工作,电源效率≥90%。

业务支持能力

- 业务类型:支持TDM(E1/T1)、ATM、以太网、专线(L2VPN/L3VPN)等多业务承载,通过CES(电路仿真)实现TDM over IP,抖动≤0.1ms;支持VPLS(虚拟专用局域网业务),MAC地址表≥16K。

- IPv6支持:双栈协议(IPv4/IPv6),转发性能无下降;支持SRv6(分段路由v6),业务路径编程灵活,SID(段标识符)深度≥10层。

- 时钟与OAM:支持NTP/PTP/SSM多时钟源,支持BFD(双向转发检测)、LMAP(链路、管理、维护协议)端到端故障检测,检测时间≤10ms。

管理与安全参数

- 管理协议:支持SNMPv3、NETCONF、YANG,支持SDN(软件定义网络)控制器南向接口(如OpenFlow、P4),实现集中管控;网管系统支持≥10万设备管理,拓扑发现时间≤5分钟。

- 安全特性:支持ACL(访问控制列表)、IPSec VPN加密(AES-256)、端口隔离,防DDoS攻击能力≥10Gbps;支持零信任架构,设备接入需双因素认证。

典型设备参数对比表

| 参数类别 | 接入层设备 | 汇聚层设备 | 核心层设备 |

|---|---|---|---|

| 端口类型 | 24×GE/4×10GE | 48×GE/8×100GE | 32×100GE/8×400G |

| 转发性能 | ≥20Mbps | ≥100Mbps | ≥10Tbps |

| 保护倒换时间 | ≤50ms(环网) | ≤50ms(环网) | ≤50ms(FRR) |

| 同步精度 | ≤1.5μs(SyncE) | ≤1μs(1588v2) | ≤0.5μs(1588v2) |

| 时延 | ≤10ms(L2转发) | ≤5ms(L2转发) | ≤3ms(L3转发) |

| 功耗 | ≤200W | ≤800W | ≤3000W |

相关问答FAQs

Q1:IP RAN与PTN(分组传送网)的主要区别是什么?

A1:IP RAN和PTN均基于分组技术,但IP RAN更侧重移动承载场景,支持IP路由协议(如OSPF、BGP),灵活性高;PTN则以TDM over IP为核心,强调L2隧道(如MPLS-TP),时延和同步性能更优,IP RAN适合多业务融合承载,PTN更适合传统移动网络回传。

Q2:5G时代对IP RAN同步参数有哪些新要求?

A2:5G对同步精度要求大幅提升:基站间同步需满足±1.5μs(TDD)和±130ns(FDD),需采用1588v2主从时钟+SyncE混合方案;核心设备需支持时间戳硬件处理(如PTP Boundary Clock),时间戳分辨率≤8ns,且同步链路需冗余设计(双路径保护)。