集成电路研发是现代信息技术的核心驱动力,其技术发展水平直接决定了国家在数字经济时代的竞争力,作为将大量电子元器件集成在单一芯片上的高科技产物,集成电路的研发涉及材料科学、半导体物理、电路设计、制造工艺、封装测试等多个学科领域,是一个技术密集、资金密集、人才密集的系统性工程,当前,随着5G通信、人工智能、物联网、云计算等新兴应用的快速崛起,集成电路研发正朝着更小制程、更高性能、更低功耗、更强功能的方向不断突破,其技术复杂度和创新难度也呈指数级增长。

在集成电路研发的早期阶段,关键技术突破往往依赖于材料与器件的创新,半导体材料是集成电路的基石,从早期的锗材料到目前主流的硅材料,再到第三代宽禁带半导体材料如碳化硅(SiC)、氮化镓(GaN),材料的革新不断推动着芯片性能的提升,碳化硅功率器件具有耐高压、高效率、耐高温等优势,在新能源汽车、光伏逆变器等领域已实现规模化应用;氮化镓器件则凭借高频特性,在快充、5G基站电源等场景展现出巨大潜力,在器件结构方面,传统的平面晶体管已逐渐被FinFET(鳍式场效应晶体管)和GAAFET(环绕栅极场效应晶体管)等三维结构取代,通过增加栅极对沟道的控制能力,有效抑制了漏电流,使得7纳米及以下制程节点的量产成为可能,台积电、三星等代工厂已率先推进3纳米、2纳米工艺的研发,采用纳米片(Nanosheet)或纳米线(Nanowire)等新型沟道结构,进一步提升了晶体管的驱动电流和开关速度。

电路设计技术是集成电路研发的另一核心环节,其目标是在有限的芯片面积内实现复杂功能的优化设计,随着系统级芯片(SoC)设计规模的不断扩大,设计复杂度已从千万级晶体管提升至百亿级,传统的手工设计方法已无法满足需求,电子设计自动化(EDA)工具成为不可或缺的设计平台,EDA工具能够完成逻辑综合、布局布线、仿真验证等全流程设计,大幅提升设计效率和准确性,在先进制程节点下,设计面临“功耗墙”“时序墙”等挑战,低功耗设计技术、可制造性设计(DFM)等成为研发重点,通过动态电压频率调节(DVFS)、电源门控(Power Gating)等技术可有效降低芯片功耗;而DFM技术则通过优化设计规则,确保电路在制造过程中良率的稳定,人工智能技术的引入正在变革传统设计流程,利用机器学习算法进行布局布线优化、时序分析等,可显著缩短设计周期,提升设计性能,谷歌利用AI设计的TPU芯片,在特定AI计算任务中性能远超传统CPU和GPU,展现了AI辅助设计的巨大潜力。

制造工艺技术的进步是集成电路性能提升的物理保障,其核心在于光刻、刻蚀、薄膜沉积、离子注入等关键步骤的精度突破,光刻技术被誉为“集成电路制造的灯塔”,其分辨率直接决定了芯片的制程节点,从紫外(UV)光刻到深紫外(DUV)光刻,再到极紫外(EUV)光刻,光源波长不断缩短,使得7纳米以下制程的量产成为可能,ASML公司生产的EUV光刻机是目前最先进的光刻设备,通过13.5纳米波长的极紫外光,能够实现13纳米级别的精细图形加工,刻蚀技术则用于将光刻形成的图形转移到硅片上,等离子体刻蚀、反应离子刻蚀等技术能够实现纳米级精度的图形转移,薄膜沉积技术包括化学气相沉积(CVD)、物理气相沉积(PVD)等,用于在硅片上形成绝缘层、导电层等关键结构,离子注入技术则是通过向硅片中掺入特定杂质,来改变半导体材料的导电类型,形成PN结等核心器件结构,这些工艺技术的协同发展,使得集成电路制造不断逼近物理极限,同时保持良率和成本的平衡。

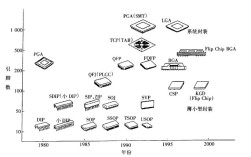

封装测试技术是集成电路研发的最后一道关卡,也是提升芯片性能和可靠性的重要环节,传统的封装技术仅能提供保护和电气连接功能,而先进封装技术则通过晶圆级封装(WLP)、2.5D封装、3D封装等手段,实现芯片间的异构集成,大幅提升系统性能,台积电的CoWoS(Chip on Wafer on Substrate)技术通过中介层将多个芯片堆叠互连,实现了高性能计算芯片的高带宽、低功耗设计;英特尔的Foveros技术则实现了3D堆叠封装,将计算单元、存储单元等不同功能的芯片垂直集成,进一步提升了集成度,在测试方面,随着芯片复杂度的增加,测试成本已占总成本的30%以上,自动测试设备(ATE)和测试方法学不断创新,基于扫描链的测试、内建自测试(BIST)等技术能够有效提升测试覆盖率;机器学习算法则被用于测试数据分析,实现故障的快速定位和预测性维护。

集成电路研发也面临着诸多挑战,随着制程节点不断缩小,量子效应、漏电流等问题日益突出,研发成本呈指数级增长,一座5纳米晶圆厂的投资额超过200亿美元,中小企业难以承担,全球供应链的不确定性加剧,关键设备和材料的“卡脖子”问题凸显,例如EUV光刻机、高端光刻胶等仍高度依赖进口,人才短缺也是制约产业发展的重要因素,集成电路研发需要大量跨学科的高端人才,包括工艺工程师、设计专家、设备工程师等,全球范围内人才竞争日趋激烈。

为应对这些挑战,全球主要国家和地区纷纷加大研发投入,推动产业链协同创新,美国的《芯片与科学法案》通过提供巨额补贴,鼓励企业在美国本土建设先进制程生产线;欧盟启动了“欧洲芯片法案”,计划投入430亿欧元,提升欧洲在全球半导体领域的竞争力;中国也将集成电路产业列为重点发展领域,通过“国家集成电路产业投资基金”等政策工具,支持全产业链的技术突破,在技术层面,异构集成、芯粒(Chiplet)等新兴技术成为突破摩尔定律限制的重要方向,通过将不同功能、不同工艺的芯粒集成封装,能够在降低成本的同时提升系统性能,AMD的Ryzen处理器采用Chiplet设计,将多个计算核心和IO核心集成在一起,实现了高性能与高性价比的平衡。

集成电路研发将继续朝着“超越摩尔”和“延续摩尔”双轨并行的方向发展,在“延续摩尔”方向,3纳米、2纳米甚至1纳米制程的研发将不断推进,新型材料(如二维材料)和新型器件结构(如隧穿晶体管)有望突破传统硅基技术的极限,在“超越摩尔”方向,通过先进封装和异构集成,将计算、存储、传感等不同功能的芯片深度融合,形成系统级解决方案,满足人工智能、自动驾驶等新兴应用的需求,绿色低碳将成为集成电路研发的重要考量,通过低功耗设计、绿色制造等技术,降低芯片的能源消耗和环境影响。

相关问答FAQs:

-

问:集成电路研发中,光刻技术的突破对整个行业有何重要意义?

答:光刻技术是集成电路制造的核心环节,其分辨率直接决定了芯片的制程节点,光刻技术的突破(如从DUV到EUV的升级)使得芯片制造能够实现更小的线宽,从而在单位面积内集成更多晶体管,提升芯片的性能和功能,先进光刻技术的应用也推动了设计、制造、封装等全产业链的技术升级,是维持摩尔定律持续发展的关键,没有光刻技术的突破,集成电路就无法向更小制程、更高集成度的方向发展,整个信息产业的发展也将受到严重制约。 -

问:在当前全球竞争格局下,我国集成电路研发面临的主要挑战有哪些?

答:我国集成电路研发面临的主要挑战包括:一是核心设备和材料对外依存度高,如EUV光刻机、高端光刻胶等关键环节仍依赖进口,存在“卡脖子”风险;二是研发投入不足,先进制程晶圆厂建设成本高昂,企业资金压力大;三是高端人才短缺,跨学科、高水平的研发人才供给不足,难以满足产业快速发展的需求;四是产业链协同不足,设计、制造、封测等环节的协同创新能力有待提升,这些挑战需要通过加强自主创新、完善产业链生态、加大人才培养和政策支持等多方面措施来逐步解决。