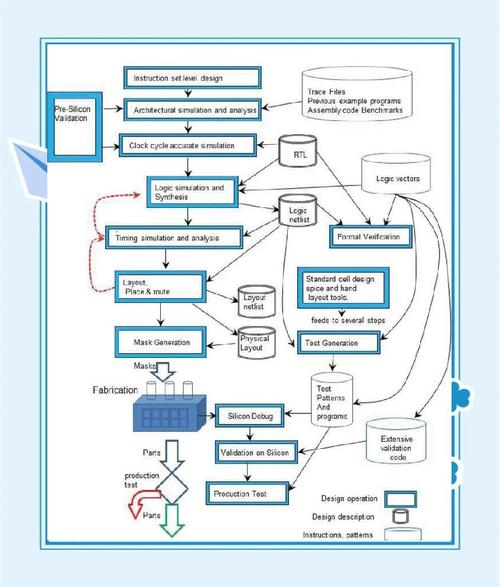

EDA技术设计流程总览

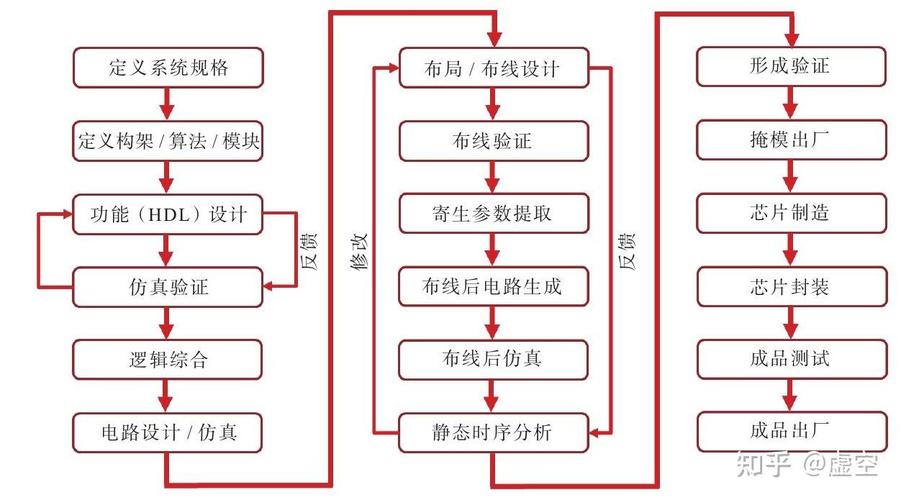

一个典型的数字集成电路设计流程可以看作一个“前端设计”和“后端设计”的结合,并贯穿始终的“验证”。

下面我们分阶段详细解释每个步骤。

系统级设计与架构定义

这是整个设计的起点,目标是定义芯片要实现的功能、性能和约束。

-

需求分析

- 目标:明确芯片的应用场景、功能需求(如处理什么数据)、性能指标(如运算速度、功耗)、成本目标以及市场定位。

- 输出:一份详细的产品需求文档。

-

架构设计与建模

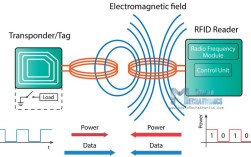

(图片来源网络,侵删)

(图片来源网络,侵删)- 目标:将高层次的需求转化为具体的系统架构,这包括选择处理器核心、确定总线架构(如AXI)、规划功能模块划分(如CPU、GPU、NPU、接口控制器等)、定义内存层次结构。

- 方法:使用高层次语言或建模工具(如SystemC, MATLAB/Simulink)来创建一个可执行的架构模型,这个模型不关心具体的实现细节,只关注功能和性能。

- 输出:架构规格书和可执行的架构模型。

-

硬件/软件协同验证

- 目标:在硬件设计开始前,验证架构模型的正确性,软件开发人员可以基于这个模型开始编写固件和驱动程序,实现软硬件的并行开发,缩短上市时间。

- 输出:经过验证的架构模型和早期版本的软件代码。

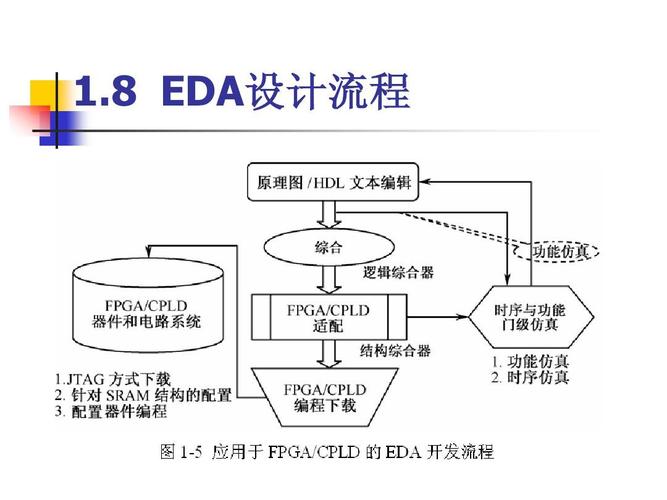

前端设计

前端设计的主要任务是完成逻辑设计,并将其转化为标准逻辑单元的网表,不关心具体的物理实现。

-

RTL设计

- 目标:将经过验证的架构模型,用硬件描述语言(HDL)实现为寄存器传输级代码,这是将设计思想转化为具体电路描述的关键一步。

- 工具:主要使用 Verilog 或 VHDL。

- 输出:RTL设计代码(

.v,.sv,.vhd文件)。

-

功能仿真

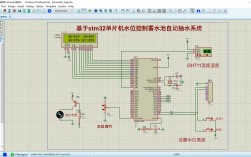

(图片来源网络,侵删)

(图片来源网络,侵删)- 目标:在综合之前,对RTL代码进行逻辑功能的正确性验证,确保代码的行为与设计意图完全一致,不考虑任何物理延迟。

- 方法:使用测试平台向RTL设计输入激励,检查输出结果是否正确。

- 工具:EDA仿真器,如 VCS (Synopsys), Questa (Siemens EDA, 前身为Mentor), Xcelium (Cadence)。

- 输出:功能仿真波形报告和验证结果。

-

逻辑综合

- 目标:将RTL代码自动转换为由标准逻辑门电路(与、或、非、触发器等)构成的门级网表,这个过程会根据指定的工艺库,将抽象的RTL行为描述映射成具体的、可物理实现的逻辑单元。

- 输入:RTL代码、综合约束文件(.sdc,包含时序、面积等要求)、标准工艺库。

- 工具:综合工具,如 Design Compiler (Synopsys), Genus (Cadence)。

- 输出:门级网表文件(通常是 EDIF 或 Verilog 格式)。

-

门级仿真

- 目标:对综合后的网表进行仿真,以验证综合过程是否引入了逻辑错误,仿真会考虑标准单元的延迟信息(零延迟或反标注延迟)。

- 输出:门级仿真报告,确保综合后的网表功能与RTL一致。

后端设计

后端设计的主要任务是将前端产生的网表转化为可以在硅片上物理制造的版图,并确保设计满足时序、功耗和面积等所有约束。

-

规划

- 目标:为物理设计制定一个宏观的“蓝图”。

- Die (芯片) 尺寸规划:根据预估的模块大小和I/O数量,确定最终的芯片尺寸。

- 布局规划:大致确定各个功能模块在芯片上的位置,规划电源网络和时钟树的大致走向。

- 时序预算:将整个芯片的时序要求分配到各个模块和路径上。

-

布局

- 目标:根据布局规划的指导,将网表中的所有标准单元精确地放置在芯片的指定位置,以优化连线长度、减少拥塞。

- 工具:物理设计工具,如 Innovus (Cadence), ICC/ICC2 (Synopsys)。

- 输出:带有物理位置信息的布局文件。

-

时钟树综合

- 目标:为芯片设计一个低 skew(偏差)、低功耗的时钟网络,时钟信号需要同步地到达触发器的时钟端,以避免建立/保持时间违例。

- 方法:在布局的基础上,插入大量的缓冲器和驱动器,构建出平衡的时钟树。

- 输出:插入时钟树后的布局数据。

-

布线

- 目标:在已经放置好的单元之间,按照设计规则,精确地画出所有金属连线,完成电气连接。

- 过程:通常分为全局布线(大致确定连线路径)和详细布线(精确绘制每条金属线)。

- 输出:完整的版图数据。

-

物理验证

- 目标:检查生成的版图是否符合制造工艺的要求和设计规则。

- 包含两个关键子步骤:

- DRC (Design Rule Check):检查版图的几何尺寸、间距、密度等是否符合代工厂的工艺规范。

- LVS (Layout Versus Schematic):将提取出的版图网表与原始的逻辑网表进行比较,确保电气连接完全一致。

- 工具:物理验证工具,如 Calibre (Siemens EDA), Pegasus (Cadence)。

- 输出:DRC/LVS报告,必须无致命错误才能流片。

-

参数提取

- 目标:从最终的版图中提取出精确的电阻、电容和寄生电感参数,这些参数会严重影响电路的时序和功耗。

验证与签核

这个阶段贯穿前后端设计,但在后端设计完成后进入最关键的“签核”验证阶段。

-

静态时序分析

- 目标:在不运行仿真的情况下,通过计算路径上的延迟,快速检查整个芯片是否存在时序违例(不满足建立/保持时间),这是流片前验证时序正确性的唯一且最高效的方法。

- 输入:门级网表、SDC约束、提取出的寄生参数。

- 工具:STA工具,如 PrimeTime (Synopsys), Tempo (Siemens EDA)。

- 输出:详细的STA报告,必须显示所有时序路径均满足要求。

-

最终仿真

- 目标:在考虑了最真实的工艺、电压、温度以及寄生参数(后仿真)的情况下,进行一次最终的、最精确的功能仿真,确保芯片在真实环境中能正常工作。

- 输出:最终仿真波形报告。

制造与测试

-

生成GDSII文件

- 目标:将最终验证通过的版图数据转换为制造厂(如台积电、三星)能够直接用于光刻的GDSII格式文件,这是EDA流程的最终输出物。

-

流片

- 目标:将GDSII文件发送给晶圆代工厂,开始实际的芯片制造过程(光刻、刻蚀、掺杂等)。

-

测试与封装

- 目标:制造出的晶圆经过切割、封装,并进行测试,以筛选出有缺陷的芯片,并确保良品的功能和性能符合设计规格。

EDA技术的设计流程是一个高度迭代、环环相扣的系统工程,从抽象的系统模型开始,经过RTL设计、综合、物理实现,到最终的制造测试,每一步都依赖于前一步的输出,并且每一步都有专门的EDA工具和验证方法来确保设计的正确性,这个流程的复杂性和精密性,正是现代集成电路能够集成数百亿晶体体的关键所在。