什么是IC封装测试?

在理解设备之前,首先需要明白IC封装测试是什么。

一颗刚刚从晶圆厂制造出来的芯片,只是一个裸露的、脆弱的硅片,上面有无数微小的电路和焊点,它还不能直接使用。封装测试就是将这个裸片进行一系列处理,使其成为可以安装到电路板上的完整元器件的过程。

这个过程主要分为两大部分:

-

封装:

- 目的: 保护脆弱的裸片免受物理、化学和环境损害;将芯片的I/O(输入/输出)引脚通过导线连接到封装外壳的引脚上,以便与外部电路连接;帮助散热。

- 流程: 芯片粘贴 -> 引线键合 -> 塑封 -> 打印标记 -> 切筋成型 -> 最终电性测试。

- 关键设备: 固晶机、引线键合机、塑封机、打标机、切筋成型机等。

-

测试:

(图片来源网络,侵删)

(图片来源网络,侵删)- 目的: 验证芯片的功能、性能和可靠性是否符合设计规格,剔除有缺陷的芯片,确保交付给客户的是合格产品。

- 分类:

- 中测: 在封装完成但尚未切割分离单个芯片时进行,也叫“探针测试”或“晶圆级测试”。

- 终测: 在单个芯片被封装、切割、成型后,作为独立元器件进行最终测试。

- 关键设备: 测试机、分选机、探针台。

核心封装测试设备技术详解

下面我们重点介绍封装和测试环节中最核心、技术含量最高的几类设备。

(一) 封装核心设备

-

固晶机

- 功能: 将裸片精确地粘贴到封装基板或引线框架上,这是封装的第一步,精度要求极高。

- 关键技术:

- 视觉对位技术: 高分辨率相机和图像处理算法,确保芯片被精确放置在预定位置,偏差通常在微米级别。

- 精密运动控制: 使用高精度伺服电机和导轨,实现XYZ三轴的快速、准确定位。

- 胶量控制: 精确控制底部填充胶或银浆的涂布量,确保粘贴牢固且无溢出。

- 芯片拾取: 使用真空吸嘴或特殊夹具,安全地拾取和放置脆弱的裸片。

-

引线键合机

- 功能: 使用极细的金线、铜线或银线,将芯片上的焊盘与封装引脚连接起来,形成电信号通路,这被称为“芯片的神经”。

- 关键技术:

- 键合技术:

- 球焊: 线材末端先形成小球,在热、超声波和压力下与焊盘连接,适用于大多数芯片。

- 楔焊: 线材以楔形压在焊盘上,适用于更精细的间距。

- 高速高精度运动控制: 焊线头需要在毫秒级时间内完成复杂的弧线运动,路径规划算法至关重要。

- 弧形控制技术: 精确控制每根线的弧形高度和形状,避免线与线之间短路,并保证可靠性。

- 在线检测: 内置摄像头实时监测焊点质量(如焊球大小、弧形),自动剔除不良品。

- 键合技术:

-

塑封机

(图片来源网络,侵删)

(图片来源网络,侵删)- 功能: 将完成引线键合的框架/基板包裹在环氧树脂等塑封材料中,形成我们常见的黑色或绿色外壳。

- 关键技术:

- 材料混合与注射: 精确控制环氧树脂的混合比例、预热温度和注射压力,确保无气泡、无分层。

- 模具温度控制: 高精度的温控系统,确保塑封材料均匀固化,防止因应力导致芯片或引线损坏。

- 自动化传送: 将框架自动送入模具、取出成品,实现全自动化生产。

(二) 测试核心设备

测试环节的设备是技术壁垒最高的部分,尤其是测试机,其研发和制造能力直接反映了一个国家或地区的半导体产业实力。

-

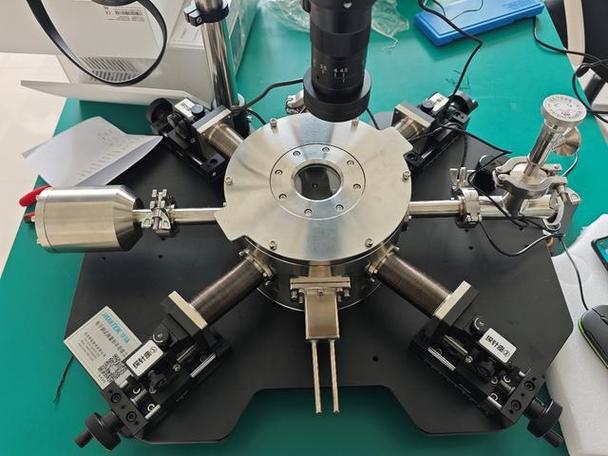

探针台

- 功能: 用于中测,将晶圆固定在载台上,精密移动探针卡,使其接触到晶圆上每个芯片的焊盘,从而进行电性测试。

- 关键技术:

- 晶圆承载与传输: 真吸盘或静电卡盘固定晶圆,防止划伤,自动上片/下片系统。

- 超精密XY工作台: 带有光栅尺,实现微米级的定位精度,确保探针能准确对准每个芯片的微小焊盘。

- 探针卡技术: 探针卡是测试的“接口”,由成千上万根微探针组成,技术复杂且成本高昂,其设计和制造是关键。

- 环境控制: 部分高端测试需要在恒温、暗室环境下进行,以消除温度和光线对芯片性能的影响。

-

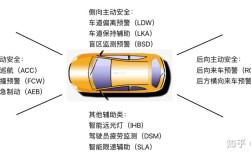

分选机

- 功能: 用于终测,将封装好的芯片从编带/托盘中逐一取出,测试台进行测试后,根据结果将芯片分拣到不同的料管或托盘中(如:好品、坏品、不同性能等级)。

- 关键技术:

- 高速拾取与放置: 使用真空吸嘴,以极高的速度(可达每秒数十颗)准确无误地拾取和放置芯片。

- 视觉识别与对位: 识别芯片上的标记(如激光印字),并将芯片精确地放置到测试探针上。

- 多通道并行测试: 现代分选机可以同时测试多个芯片,大幅提升测试效率。

- 编带技术: 将测试合格品自动编入载带和料盘,方便客户后续自动化生产。

-

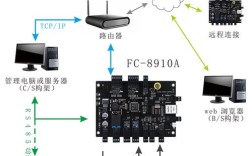

测试机 - 测试环节的“大脑”

- 功能: 这是整个测试环节的核心,它向芯片施加输入信号,并测量芯片的输出响应,判断其功能、性能(如速度、功耗)和参数是否符合设计规格。

- 关键技术(也是壁垒所在):

- 测试向量生成: 如何设计出能“考倒”芯片的“试卷”(即测试程序和向量),这需要深厚的半导体设计知识和验证经验。

- 高精度测量单元: 能够精确测量纳安级电流、微伏级电压,并支持高速信号(数GHz)的生成和捕获。

- 并行测试技术: 在一台测试机上同时测试多个芯片,通过多通道卡、多资源卡实现,是降低单颗芯片测试成本的关键。

- 硬件架构: 采用模块化设计,由电源、测量单元、数字功能单元、存储器单元等组成,需要强大的硬件设计和系统集成能力。

- 软件生态系统: 提供完整的测试开发、调试和执行环境,通常与EDA工具链紧密集成。

技术发展趋势

- 高密度与高精度: 随着芯片I/O数量增多、间距变小,设备(尤其是固晶机、键合机、探针台)的定位精度和稳定性要求越来越高。

- 高速与高效率: 测试和封装环节是成本大头,设备必须更快,通过并行化、自动化来提高吞吐量,降低单位成本,多通道测试、多晶圆并行探针台。

- 先进封装集成: 从传统封装转向2.5D/3D封装、扇出型封装等,这要求设备能处理更复杂的结构(如硅中介层)、更薄的芯片和更精细的材料。

- 智能化与数据驱动:

- AI应用: 利用机器视觉进行缺陷检测,利用AI算法优化键合路径、测试向量等。

- 大数据分析: 收集和分析设备运行数据、测试数据,实现预测性维护、工艺参数优化和良率提升。

- 绿色与节能: 降低设备功耗,减少化学品使用,符合环保要求。

主要设备供应商

- 测试机:

- 国际巨头: Teradyne (泰瑞达), Advantest (爱德万),这两家占据了全球高端测试机市场90%以上的份额。

- 国内新兴力量: 华峰测控、长川科技等,正在从模拟/电源类测试机等中低端市场切入,并逐步向数字、射频等高端领域发展。

- 分选机:

- 国际巨头: Teradyne, Advantest, Cohu (科休)。

- 国内供应商: 长川科技、文一科技等。

- 探针台:

- 国际巨头: Tokyo Electron (TEL), FormFactor, MPI。

- 国内供应商: 中科飞测、长川科技等,主要在国产化替代方面取得进展。

- 封装设备:

- 国际巨头: ASM Pacific (ASMPT), Kulicke & Soffa (K&S), Yamaha Motor (雅马哈)。

- 国内供应商: 长川科技、通富微电(部分自产)、新益昌等,在固晶机、键合机等设备上已具备较强竞争力。

IC封装测试设备技术是一个集光学、精密机械、自动化控制、电子测量和软件算法于一体的综合性高科技领域,它是连接设计与产品的桥梁,其技术水平直接决定了芯片的质量、成本和上市时间,随着芯片制造工艺不断演进,对封装测试设备的要求也日益严苛,技术创新和国产化替代将是未来很长一段时间内的主旋律。