微电子封装技术 复习大纲

微电子封装技术是连接芯片(裸片)与外部系统的桥梁,其核心目标是保护芯片、实现电气连接、散热管理以及尺寸小型化。

第一部分:基础概念与重要性

什么是微电子封装?

- 定义:将制造好的半导体芯片(裸片, Die)与基板、引线框架、外壳等材料组合在一起,并实现芯片与外部电路电气和机械连接,最终形成一个完整、可靠、功能性的电子元器件的过程。

- 核心功能(四大支柱):

- 保护:保护脆弱的芯片免受物理损伤、湿气、离子污染物、辐射等外界环境的侵害。

- 电气连接:通过键合线、倒装焊等技术,实现芯片上的焊盘与封装外部引脚之间的信号、电源和地线连接。

- 散热管理:将芯片工作时产生的高效传导出去,防止芯片因过热而失效。

- 尺寸与集成:将芯片和必要的辅助元件封装在尽可能小的体积内,并实现更高的系统集成度(如SiP)。

封装在产业链中的位置

设计 -> 晶圆制造 -> **封装测试** -> 系统集成

封装测试是晶圆制造完成后的关键后道工序,直接决定了芯片的最终性能、可靠性和成本。

封装技术的演进(非常重要!)

理解技术演进的驱动力:更高性能、更高集成度、更小尺寸、更低成本。

| 时代 | 封装形式 | 主要特点/技术 | 缩写/名称 |

|---|---|---|---|

| 早期 | 双列直插式封装 | 引脚从两侧引出,通孔插装 | DIP |

| 80-90年代 | 表面贴装技术 | 引脚从四边引出,体积更小 | QFP, PLCC |

| 90年代 | 球栅阵列封装 | 底部焊球阵列,I/O数量激增,性能提升 | BGA |

| 21世纪初 | 芯片尺寸封装 | 封装尺寸接近芯片尺寸,体积小 | CSP |

| 当前主流 | 球栅阵列/芯片级封装 | BGA的改进,如堆叠BGA | PBGA, TBGA |

| 当前主流 | 晶圆级封装 | 在整片晶圆上进行封装,再切割,成本和性能优势 | WLP |

| 当前前沿 | 5D/3D封装 | 通过硅通孔等技术在垂直方向堆叠芯片,实现超高集成 | 5D (e.g., CoWoS), 3D (e.g., TSV, SiP) |

第二部分:核心封装技术详解

芯片与基板的连接技术(互连技术)

这是封装的灵魂,决定了电气性能和散热效率。

| 技术名称 | 原理 | 优点 | 缺点 | 主要应用 |

|---|---|---|---|---|

| 引线键合 | 使用极细的金线或铜线,将芯片焊盘与基板/引线框架焊盘热压/超声焊接。 | 技术成熟、成本低、工艺灵活。 | 互连长度长,信号延迟和寄生参数大,散热受限。 | 绝大多数传统封装,如QFP, DIP, 大部分BGA。 |

| 载带自动焊 | 使用铜制带状引线,通过热压或超声焊连接。 | 适合I/O数量多、间距小的芯片,高频性能优于WB。 | 基板成本较高,不适合大功率芯片。 | CPU, GPU, FPGA等高性能芯片。 |

| 倒装焊 | 将芯片有源面朝下,通过芯片底部的焊球直接与基板焊盘连接。 | 最短互连路径,优异的电气性能和散热性能。 | 需要凸点工艺,成本较高,对准要求高。 | 高性能CPU/GPU, 移动处理器, 摄像头传感器。 |

基板技术

基板是芯片的“载体”和“布线平台”。

- 有机基板:

- 材料:环氧树脂玻璃纤维(如FR-4)。

- 优点:成本低,适合大批量生产。

- 缺点:热膨胀系数与硅芯片不匹配,散热性能较差,高频信号损耗大。

- 应用:中低端BGA, PBGA。

- 陶瓷基板:

- 材料:氧化铝(Al₂O₃)、氮化铝。

- 优点:热膨胀系数与硅接近,散热性能极佳,高频性能好,可靠性高。

- 缺点:成本高,重量大,易脆。

- 应用:高功率器件(如IGBT, LED),航空航天,军事领域。

- 硅基板:

- 材料:高阻硅。

- 优点:与芯片材料完全匹配,可实现超精细布线,是5D/3D封装的核心。

- 缺点:成本极高,是基板中的“奢侈品”。

- 应用:高端CPU/GPU的2.5D封装中介层。

先进封装技术

这是当前考试和行业的热点。

-

晶圆级封装

- 定义:在晶圆切割成单个芯片之前,就对整片晶圆进行封装和测试。

- 优点:

- 尺寸小:封装尺寸≈芯片尺寸。

- 成本低:批量化生产,效率高。

- 性能好:WLP可以结合倒装焊技术。

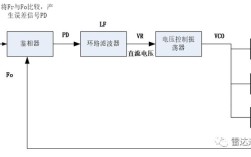

- 代表技术:硅通孔,在晶圆上钻孔并金属化,实现芯片正反面的垂直电气连接。

-

5D 封装

- 结构:多个芯片并排放置在一个硅中介层上,中介层通过TSV技术连接到基板。

- 核心:硅中介层,它像一个“转接板”,让不同工艺、不同功能的芯片(如CPU和HBM)可以紧密集成。

- 优点:解决了不同芯片直接对准和布线的难题,提供高带宽。

- 例子:AMD的Ryzen CPU + 高带宽内存 的封装。

-

3D 封装

(图片来源网络,侵删)

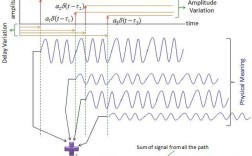

(图片来源网络,侵删)- 结构:将多个芯片在垂直方向上直接堆叠起来,通过TSV或微凸点实现层间互连。

- 核心:TSV (硅通孔) + 微凸点。

- 优点:极致的集成度,缩短信号路径,功耗更低。

- 例子:手机内存堆叠,图像传感器堆叠。

-

系统级封装

- 定义:将不同功能的芯片(处理器、存储器、模拟芯片、无源元件等)集成在一个封装体内,形成一个功能完整的“系统”。

- 特点:“More than Moore”,超越了摩尔定律的单纯尺寸缩小,强调系统功能的集成。

- 例子:智能手表里的SoP,将处理器、传感器、电源管理芯片等封装在一起。

第三部分:关键材料与制造流程

关键材料

- 封装材料:环氧树脂模塑料,用于保护芯片和内部结构。

- 基板材料:有机(FR-4)、陶瓷(Al₂O₃, AlN)、硅。

- 键合材料:金线、铜线、合金焊球(如SnAgCu无铅焊料)。

- 底部填充胶:注入BGA和基板之间,缓解热应力,提高可靠性。

典型封装制造流程(以BGA为例)

- 背面减薄:将晶圆背面磨薄,以满足封装后的厚度要求。

- 晶圆切割:将整片晶圆切割成独立的芯片。

- 芯片贴装:将芯片固定在基板的中央。

- 键合:使用WB或FC技术连接芯片和基板。

- 注塑/模塑:用环氧树脂包裹芯片和键合线,形成保护体。

- 打标:在封装表面印上型号、批次等信息。

- 切筋成型:修剪多余部分,形成最终的封装外形。

- 电镀:在封装底部焊盘上镀上防氧化和易焊接的金属层。

- 最终测试:对封装好的芯片进行功能和性能测试。

第四部分:可靠性

封装的可靠性是产品能否长期稳定工作的关键。

- 主要失效模式:

- 热疲劳:芯片、封装材料、基板的热膨胀系数不匹配,在温度循环中产生应力,导致焊球开裂或分层。

- 湿气敏感:封装材料吸收湿气,在回流焊高温下气化,导致封装“爆米花”分层。

- 电迁移:在大电流密度下,金属原子移动,导致线路断路或短路。

- 可靠性测试:

- 温度循环:在极端高低温之间循环,测试抗热疲劳能力。

- 高温存储/工作寿命:在高温下长时间测试。

- 湿度敏感等级测试:测试芯片对湿气的敏感程度。

第五部分:未来趋势

- 异构集成:将不同材料、不同工艺的芯片(如硅、III-V族化合物、MEMS)集成在一起,实现超越单一技术的功能。

- 芯粒:将复杂的功能芯片分解成多个功能更专一的小芯片,通过先进封装技术(如2.5D/3D)集成,降低成本,提高良率。

- 高密度/高I/O:随着AI、5G、HPC的发展,对封装的I/O数量和带宽要求越来越高。

- 先进散热技术:如液冷、嵌入式散热器等,解决芯片“热墙”问题。

复习策略与考点预测

- 抓住主线:以“四大功能”为纲,理解所有技术都是为了更好地实现这四个功能。

- 对比记忆:将WB、FC、TAB等互连技术,以及有机/陶瓷/硅基板进行对比,记住它们的优缺点和适用场景。

- 掌握演进:从DIP到3D封装,理解每一代技术出现的驱动力和解决的问题,这是论述题的常客。

- 关注前沿:WLP, 2.5D (TSV, Interposer), 3D (TSV, Stacking), SiP, Chiplet 这些是必考名词,务必理解其定义、结构和优势。

- 理解可靠性:记住热膨胀系数不匹配是封装失效的核心物理原因,以及常见的测试方法。

- 联系实际:想一想你身边的电子产品,比如手机里的SoP、电脑CPU的封装,它们分别应用了哪些技术?

祝你复习顺利,考试成功!