核心挑战概览

如果用一句话概括,当今电子测试技术的核心难题是:测试对象(芯片、系统)的复杂性、集成度和工作频率呈指数级增长,而传统测试方法的成本、速度和能力已无法跟上其发展的步伐,形成了日益严峻的“测试瓶颈”。

下面我们从几个具体领域展开分析:

芯片级测试:先进工艺的极限挑战

这是最直接、最前沿的挑战,主要围绕先进制程的芯片测试。

测试成本急剧攀升

- 问题:随着摩尔定律进入3nm、2nm甚至更先进的工艺节点,芯片的研发和制造成本已经达到了天文数字,测试成本在整个芯片成本中的占比也越来越高,测试设备本身极其昂贵(一台高端ATE测试机可能价值数千万美元),测试开发时间长,测试时间长,导致测试成本成为芯片能否盈利的关键因素。

- 举例:一颗7nm的SoC芯片,其测试成本可能高达数百万美元,占其总成本的15%-20%甚至更高。

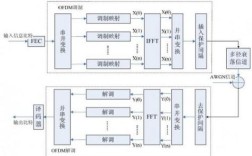

测试频率与带宽的“鸿沟”

- 问题:芯片内部的工作频率已经进入GHz甚至更高范围(如PCIe 6.0/7.0的信号速率高达64 GT/s),测试设备与芯片之间的物理连接(探针卡、测试板、线缆)会引入信号完整性问题,如串扰、损耗、反射和阻抗不匹配,这导致测试信号的保真度急剧下降,测试设备难以准确、无失真地捕获和激励如此高速的信号,形成了“测不准”或“测得慢”的困境。

- 挑战:需要开发新的探针技术(如射频探针)、更高质量的测试板和线缆,以及先进的信号处理算法来补偿失真。

先进制程的物理与电气特性

- 问题:

- 漏电流与功耗:先进工艺的晶体管尺寸极小,漏电流问题严重,导致芯片在静态下功耗也可能很高,测试时,如何在不损坏芯片的前提下,精确测量和验证其动态功耗和静态功耗,是一个巨大挑战。

- 工艺变异:在原子级别,工艺的随机性(如线宽的微小差异)会导致芯片与芯片之间、甚至芯片内部不同单元之间性能存在差异(被称为“Within-Die Variation”),这使得传统的基于“规格”的测试方法失效,需要更复杂的统计测试方法。

- 自热效应:高密度集成导致工作时热量集中,芯片温度会动态变化,进而影响其电气性能,测试必须在模拟真实工作温度的条件下进行,这对测试环境提出了苛刻要求。

人工智能芯片的测试新范式

- 问题:AI芯片(如NPU、TPU)的架构与传统CPU/GPU完全不同,其核心是大量的计算单元和片上存储器(如SRAM),测试重点不再是单个逻辑门的正确性,而是矩阵运算的精度、吞吐量和能效。

- 挑战:

- 如何生成测试向量:传统的基于故障模型的测试向量生成方法不适用,需要开发能覆盖各种神经网络模型和数据集的“类数据”测试向量,以验证芯片的泛化能力。

- 如何定义“通过/失败”:对于计算结果,通常允许一定的误差范围,如何科学地定义这个误差范围,并高效地验证海量输出结果,是测试的关键。

- 性能测试:测试其每秒万亿次运算、能效比等关键指标,需要全新的测试方法和性能分析工具。

系统级测试:异构集成与高速互联的复杂性

当多个芯片(如CPU、GPU、AI芯片、内存)封装在一起形成一个系统时,测试的复杂性呈几何级数增长。

异构集成与芯粒的测试

- 问题:为了突破单芯片的物理极限,业界越来越多地采用“芯粒”技术,将不同工艺、不同功能的“小芯片”通过先进封装(如CoWoS, 2.5D/3D IC)集成在一个封装内。

- 挑战:

- 测试访问:如何物理上接触到每个芯粒进行测试?需要在设计阶段就规划好“测试接入点”,但这会增加设计和封装的复杂性。

- 芯粒间互连测试:芯粒之间的互连是新的故障源,需要专门的测试方法来验证这些高速、高密度的互连链路是否正常。

- 芯粒的“已知良好芯粒”筛选:在集成前,如何确保每个芯粒本身是“已知良好”的?这需要在芯粒级别进行高效、低成本的测试。

高速串行总线的测试

- 问题:现代系统内部和外部都依赖于高速串行总线,如PCIe, DDR5, CXL, HDMI 2.1等,这些总线的速率极高,对信号完整性要求极为苛刻。

- 挑战:

- 一致性测试:不仅要测试功能是否正确,还要测试其是否符合协议规范,这需要极其昂贵的协议分析仪和误码率测试仪。

- 信道表征:测试的重点不再是“通/断”,而是信道的“质量”,如眼图、抖动、误码率等,这需要高精度的示波器和复杂的信号分析软件。

- 调试困难:当系统出现高速总线故障时,定位问题根源(是芯片问题、PCB布线问题、连接器问题还是电源问题?)非常困难,需要强大的调试工具。

电源完整性与信号完整性

- 问题:芯片和系统功耗巨大且动态变化,对电源的稳定性和纯净度要求极高,高速信号会向电源和地平面注入噪声,形成“电源噪声”,反过来又会干扰信号传输,形成恶性循环。

- 挑战:

- 如何测量:需要使用高带宽的差分探头和电源探头来精确捕获电源轨上的微小噪声和瞬态响应。

- 如何分析:如何将电源噪声与系统性能下降或错误关联起来,并进行根源分析,是系统级调试的一大难题。

软硬件协同测试:系统软件定义的复杂性

现代电子系统,尤其是智能设备,其功能越来越多地由软件定义,这使得测试的边界变得模糊。

软硬件交互的“灰色地带”

- 问题:很多系统故障并非纯粹的硬件缺陷,也非纯粹的软件Bug,而是软硬件交互时产生的未知问题,一个特定的软件操作序列可能导致硬件出现异常功耗或时序违规。

- 挑战:传统的硬件测试和软件测试团队是分离的,如何建立一个统一的测试平台,能够同时驱动硬件和软件,并捕捉到这种跨领域的交互故障,是巨大的管理和技术挑战。

AI驱动的自我测试与诊断

- 问题:面对海量的测试数据和复杂的故障模式,传统的基于规则和阈值的测试方法已不堪重负。

- 挑战:如何利用人工智能和机器学习技术:

- 智能测试生成:AI可以根据系统行为自动生成更高效、更全面的测试用例。

- 异常检测:通过学习大量正常工作的数据模式,AI可以自动识别出微小的、以前难以发现的异常。

- 故障根因分析:当测试失败时,AI可以快速分析海量日志和波形数据,定位到最可能的故障原因,大大缩短调试时间。

总结与未来方向

当今电子测试技术的难题可以归纳为“高、精、尖、广”四个字:

- 高:高频、高速、高集成度。

- 精:对精度的要求越来越高(功耗、时序、信号质量)。

- 尖:面向最尖端的工艺和架构(3nm、Chiplet、AI芯片)。

- 广:测试范围从单一的物理层扩展到复杂的软硬件系统层。

未来的发展方向将围绕以下几点:

- 数据驱动与AI赋能:利用大数据和AI实现智能测试、预测性维护和自动化诊断。

- 内建自测试:将更多的测试逻辑直接设计到芯片和系统中,减少对外部昂贵ATE的依赖,实现更高效的在片测试。

- 云化与协同测试:将测试资源、数据和专家知识上云,实现全球协同开发和测试,降低成本,提高效率。

- 新的测试理论与方法:针对AI、量子计算等颠覆性技术,需要从底层构建全新的测试理论、故障模型和验证方法。

电子测试技术正站在一个变革的十字路口,它不再是产品开发流程的末端,而是与设计、制造同等重要的核心环节,其创新能力和水平直接决定了一个国家或企业在未来科技竞争中的成败。