这不仅仅是一个数字(如5nm),而是一个涉及晶体管架构、材料、设计方法学和生态系统的复杂技术体系,当前,ASIC技术正处于一个关键的转折点,以应对摩尔定律放缓和算力需求爆炸的双重挑战。

以下是当前ASIC最新技术工艺的几个核心维度:

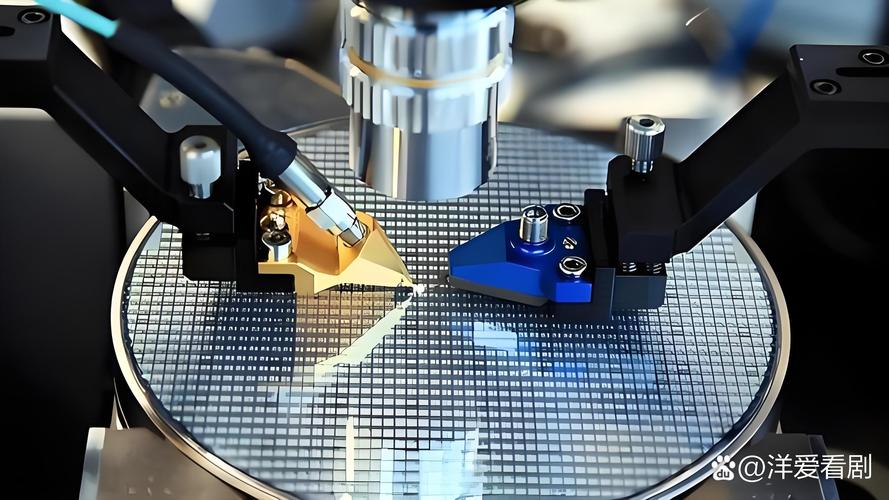

晶体管架构:从平面到3D的飞跃

这是目前最核心、最革命性的变化,传统的平面晶体管(FinFET)已经接近其物理极限,无法在更小的尺寸下有效控制漏电和维持性能,业界巨头们推出了全新的3D晶体管架构。

a. GAAFET (全环绕栅极场效应晶体管)

这是目前最主流的下一代晶体管技术,也是3nm及以下工艺的基石。

- 技术原理:与FinFET中栅极包裹“鱼鳍”状通道不同,GAAFET的栅极完全环绕着一个垂直的、纳米级的纳米片 或 纳米线 通道,电流从垂直的纳米片中流过,栅极可以360度无死角地控制通道,从而实现近乎完美的静电控制。

- 主要玩家:

- 三星:率先在3nm工艺(称为3GAE)中大规模量产GAAFET,命名为SFET(Surrounding Field-Effect Transistor)。

- 台积电:在3nm工艺(N3E)的第二阶段(N3B)引入了GAAFET,命名为GAA,并在后续的N3P、N3X等工艺中持续优化。

- 优势:

- 更高的驱动电流:更短的电流路径带来更快的开关速度。

- 更低的漏电:完美的栅极控制有效减少了漏电流,降低了功耗。

- 更强的可扩展性:为2nm、1.5nm及以下的工艺节点铺平了道路。

b. CFET (堆叠式全环绕栅极晶体管)

这是GAAFET的终极形态,是真正的3D晶体管堆叠。

- 技术原理:将N型和P型晶体管像乐高积木一样垂直堆叠在一起,形成N-P或P-N的堆叠结构,这极大地缩短了晶体管之间的连接距离,理论上可以带来最高的晶体管密度和性能。

- 现状:目前仍处于早期研发阶段,被认为是2nm或1.5nm节点的候选技术,挑战在于制造工艺的极端复杂性、良率控制和热管理。

- 意义:CFET将芯片的“2D平面布局”推向了“3D立体集成”,是延续摩尔定律的终极方向之一。

制造工艺节点:数字背后的意义

我们常说的“3nm”、“2nm”已经不再是晶体管栅极的实际长度,而是代表一个工艺代际的营销术语,其核心是上述的晶体管架构和集成密度。

- 台积电 3nm (N3系列):

- N3/N3B:首批GAAFET工艺,相比其5nm工艺,逻辑密度提升约70%,性能提升约18%,功耗降低约34%。

- N3E:优化版3nm,成本更低,性能和密度略低于N3B,适用于对成本更敏感的应用。

- N3P/N3X:持续优化的版本,N3P提升性能和密度,N3X则专注于高性能计算,提供更高的时钟频率。

- 三星 3nm (3G系列):

- 3GAE:全球首批量产的GAAFET工艺,台积电的主要竞争对手。

- 3GAP:优化版,目标与台积电的N3E竞争。

- 英特尔 20A/18A (Intel 4之后):

- Intel 20A:英特尔的“翻盘之作”,首次引入了两大革命性技术:

- RibbonFET:英特尔的GAAFET实现。

- PowerVia:背面供电技术,传统的芯片是正面供电,背面供电将电源线和信号线完全分离,电源线从晶圆背面接入,极大降低了电阻和功耗,提升了信号完整性和性能。

- Intel 18A:20A的增强版,进一步缩小晶体管尺寸,预计性能和密度将再次大幅提升,是Intel重返技术前沿的关键一步。

- Intel 20A:英特尔的“翻盘之作”,首次引入了两大革命性技术:

材料创新:硅的“左膀右臂”

为了在物理极限下继续提升性能,新材料被引入以替代传统的硅和硅氧化物。

- 栅极极化层:在GAAFET时代,传统的二氧化硅栅极介质已经不够“绝缘”,业界开始使用金属栅极,并结合高K介质材料(如HfO₂),以有效控制漏电并提高驱动能力。

- 互连材料:

- 低K介质:用于层间隔离,减少信号串扰和RC延迟。

- 铜/钴/钌互连:从传统的铝互连,到铜,再到更薄的钴,以及未来可能使用的钌,都是为了降低电阻,应对越来越细的导线带来的信号延迟问题。

- 第三代半导体:虽然主要用于功率和射频器件,但GaN(氮化镓)和SiC(碳化硅)在特定ASIC(如快充芯片、电动汽车逆变器)中展现出高压、高效率的优势,是材料创新的重要分支。

设计方法学与EDA工具:驾驭复杂性

工艺的进步带来了设计复杂性的指数级增长,没有先进的EDA(电子设计自动化)工具,先进工艺无法被有效利用。

- DTCO (Design-Technology Co-optimization):设计与工艺协同优化,在工艺开发早期,设计团队就介入,共同定义标准单元、库和规则,确保工艺能为最终产品提供最佳性能、功耗和面积。

- DFM (Design for Manufacturability):面向制造的设计,先进工艺对制造缺陷极其敏感,DFM技术通过在设计中加入冗余、调整布线规则等方式,提高芯片的良率。

- AI驱动的EDA:人工智能正在被用于芯片设计的各个环节,如逻辑综合、布局布线、物理验证等,以解决NP难问题,找到更优的解,缩短数周的流片时间。

- Chiplet (小芯片) / 2.5D/3D封装:这是应对“单片SoC”设计成本和复杂度飙升的关键策略,将一个大的ASIC芯片分解成多个功能独立的“小芯片”(如CPU、GPU、I/O Chiplet),然后通过先进封装技术(如台积电的CoWoS、InFO,英特尔的Foveros)将它们高密度地集成在一起,这种方式提高了良率、降低了成本、实现了模块化和异构集成,是当前高性能计算ASIC(如GPU、AI加速器)的主流设计范式。

应用领域的驱动:不同需求,不同技术路线

ASIC的最新技术并非“一刀切”,而是由不同的应用需求驱动的。

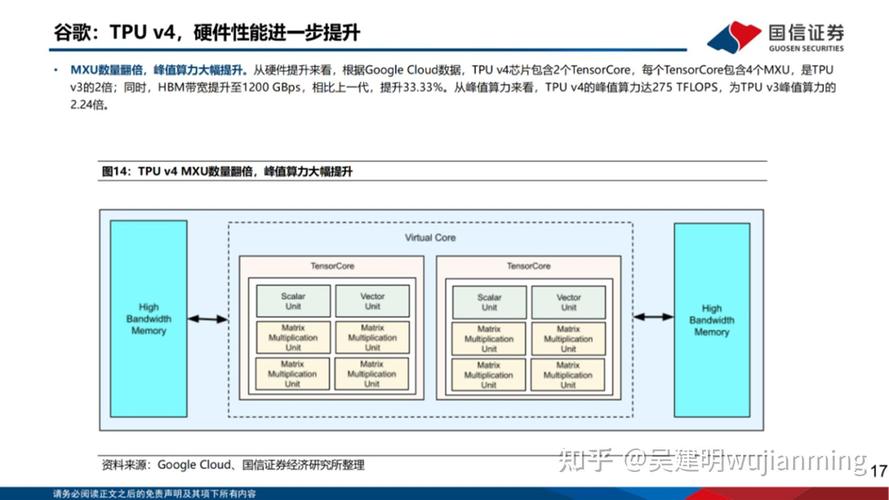

- 高性能计算 / AI训练芯片 (如NVIDIA H100, Google TPU v5):

- 需求:极致的算力、高内存带宽、低延迟。

- 技术:采用最先进的工艺(如台积电4N/5nm),大量使用Chiplet异构集成,集成HBM(高带宽内存)和高速SerDes接口,设计复杂度极高。

- 移动SoC (如Apple A17 Pro, Snapdragon 8 Gen 3):

- 需求:高性能与极致低功耗的平衡。

- 技术:采用最先进工艺(如台积电3nm),在SoC内部集成CPU、GPU、NPU、ISP等多种模块,通过大小核设计(如Performance Core + Efficiency Core)来管理功耗。

- 汽车电子芯片:

- 需求:极高的可靠性、功能安全、长期供货。

- 技术:不一定采用最前沿的工艺,而是采用成熟且经过验证的工艺(如台积电16nm/28nm),并在此基础上进行汽车级认证和加固,现在也开始向更先进的7nm、5nm演进,以满足自动驾驶对算力的需求。

- 物联网/低功耗芯片:

- 需求:超低功耗、小尺寸、低成本。

- 技术:采用成熟或更成熟的工艺(如台积电22nm/28nm ULP,甚至130nm),专注于低功耗设计和模拟/混合信号集成能力。

ASIC的最新技术工艺是一个多维度、系统性的演进,其核心可以概括为:

- 架构革命:从FinFET迈向GAAFET,为未来铺路。

- 制造突破:背面供电等技术成为新的性能增长点。

- 材料迭代:高K/金属栅、先进互连成为标配。

- 设计范式:Chiplet异构集成成为应对高复杂度和高成本的终极方案。

- AI赋能:AI+EDA成为管理设计复杂性的关键。

摩尔定律并未终结,而是以“More Moore”(延续摩尔定律,追求更小、更快、更省电)和“More than Moore”(超越摩尔定律,通过集成、新材料、异构系统实现更多功能)两条路径并行演进,而最新的ASIC工艺正是这两条路径交汇点的最佳体现。