引言:从“沙子”到“智慧”的魔法

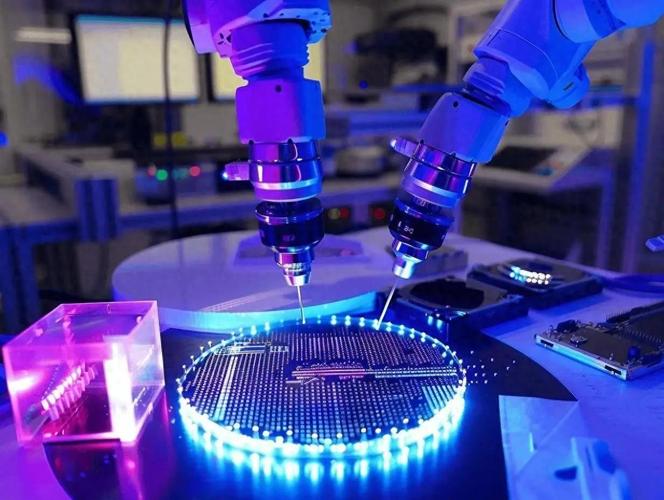

我们今天所依赖的一切——智能手机、电脑、人工智能、自动驾驶、医疗设备——其核心都是微纳米芯片,而制造这些芯片的基石,就是光刻技术。

这个过程就像是用一支“光笔”在“画板”(硅片)上,一层一层地画出极其微小的电路图,最终将成千上万个晶体管等元器件集成在一起,形成功能强大的处理器或存储器,微纳米芯片技术的进步,本质上就是光刻技术不断突破极限的历程。

第一部分:微纳米芯片技术

什么是微纳米芯片技术?

微纳米芯片技术,通常称为微电子学,是研究、设计和制造在微米(μm,10⁻⁶米)和纳米(nm,10⁻⁹米)尺度上工作的电子电路和系统的技术。

- 核心: 在一小块硅片上,集成尽可能多的晶体管,集成度越高,芯片的性能就越强,功耗越低,功能越复杂。

- 衡量标准: 制程工艺节点,例如7nm、5nm、3nm,这个数字不完全等于晶体管上某个线条的宽度,但它代表了整个制造工艺的先进程度,数字越小,通常意味着晶体管越小、密度越高、性能越好。

- 物理基础: 半导体物理,利用硅等半导体材料的特性,通过掺杂、氧化、沉积等工艺,制造出可以控制电流流动的晶体管(如MOSFET),它们是芯片最基本的开关和放大单元。

为什么追求更小的尺寸?

摩尔定律是驱动这一追求的核心动力,它预测,集成电路上可容纳的晶体管数量,约每隔18-24个月便会增加一倍,性能也将提升一倍。

- 性能提升: 晶体管更小,电子在其中跑的距离更短,开关速度更快,芯片整体运行速度就更快。

- 功耗降低: 更小的晶体管在开关时消耗的能量更少,这对于移动设备和数据中心至关重要。

- 成本降低: 在同样大小的硅片上能制造更多芯片,单个芯片的成本理论上会降低。

- 功能集成: 可以将更多功能(如CPU、GPU、内存、AI加速单元)集成到一颗芯片上,形成SoC(System on a Chip,系统级芯片)。

第二部分:光刻技术——芯片制造的“照相”与“雕刻”

如果说芯片制造是一场宏伟的建筑施工,那么光刻就是其中最重要、最精密的“画图”环节。

光刻的基本原理

光刻技术类似于传统摄影,但其精度要求高出数百万倍。

- “底片”(掩模版 Mask): 首先设计好电路的蓝图,并将其制作成一块不透明的玻璃板,上面有透光的电路图案,这就是掩模版。

- “画板”(硅片 Wafer): 作为基底,通常是高度纯化的硅片。

- “光敏涂料”(光刻胶 Photoresist): 在硅片表面均匀涂上一层对特定波长光线敏感的化学材料。

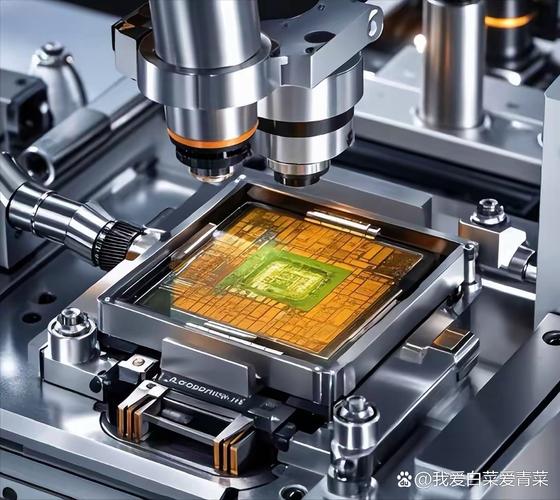

- “曝光机”(光刻机 Lithography Scanner): 这是光刻的核心设备,它将特定波长的光(如深紫外光DUV、极紫外光EUV)通过掩模版,将图案精确地投影到硅片表面的光刻胶上。

- “显影”(Development): 曝光后的光刻胶会发生化学变化,通过显影液,被光照到的部分(或未被光照的部分)被溶解,从而在光刻胶上形成了与掩模版一致的电路图案。

- “雕刻”(刻蚀 Etching): 以光刻胶为“保护罩”,通过化学或物理方法(如等离子体刻蚀)将没有被光刻胶覆盖的硅或其他材料层去除,从而将图案永久地“雕刻”到硅片上。

- “清除”(去胶 Stripping): 去除掉剩余的光刻胶,完成一层图案的转移。

这个过程需要重复数十次,每一次都添加不同的材料层(如金属连线、绝缘层),最终构建出三维的复杂芯片结构。

光刻技术的演进与挑战

为了实现更小的制程节点,光刻技术一直在不断挑战物理极限。

| 时代 | 光刻技术 | 光源波长 | 对应节点 | 核心挑战与突破 |

|---|---|---|---|---|

| 早期 | 接触式/接近式 | g-line (436nm) / i-line (365nm) | > 1μm | 简单,但分辨率低,易污染损伤。 |

| 成熟期 | 深紫外光 | KrF (248nm) | 250nm - 90nm | 光学邻近效应修正:由于光的衍射,图案会发生变形,需要预先在掩模版上做“补偿”。 |

| ArF (193nm) | 130nm - 7nm | 浸没式光刻:在镜头和硅片之间填充纯水,提高折射率,等效缩短波长,从而提升分辨率,这是延续193nm光生命力的关键。 | ||

| 当前主流 | 多重曝光 | ArF (193nm) | 7nm - 5nm | 单次曝光无法达到足够小,需要对同一层图案进行2次或4次曝光,大大增加了成本和复杂度。 |

| 尖端 | 极紫外光 | EUV (13.5nm) | 7nm及以下 | 终极武器,波长极短,可以直接实现更小节点的单次曝光,是先进制程的“必选项”。 |

| 未来探索 | 高NA-EUV | EUV (13.5nm) | 3nm及以下 | 高数值孔径镜头,进一步提高分辨率,是3nm及以下节点的关键。 |

| 纳米压印 | 无需光源 | 实验室/特定领域 | 不用光,而是用机械模具“压印”图案,分辨率极高,但量产难度大,易有缺陷。 |

光刻机的“王者”——ASML

在光刻领域,荷兰公司ASML(阿斯麦)是绝对的霸主,它不生产芯片,但它生产制造芯片最关键的设备——光刻机,尤其是最先进的EUV光刻机。

- 技术壁垒: ASML的EUV光刻机是人类工业技术的巅峰之作,集成了全球最顶尖的技术:

- 德国蔡司:提供精度以皮米(pm,10⁻¹²米)计的EUV反射镜(多达10个),镜面平整度比地球表面还要光滑得多。

- 美国Cymer:提供EUV光源,通过激光轰击锡珠产生等离子体,产生13.5nm波长的极紫外光。

- 自身系统集成:将来自全球各地的数万个精密零件整合成一个稳定、高速、超精密的复杂系统。

- 战略地位: 由于其技术的极端复杂性和战略重要性,ASML的EUV光刻机受到严格的出口管制,成为全球半导体产业链博弈的焦点。

第三部分:光刻技术的未来趋势

随着物理极限的不断逼近,光刻技术也面临着新的挑战和机遇。

- 高NA-EUV (High-NA EUV): 这是下一代光刻的明确方向,它将数值孔径从0.33提升到0.55,分辨率显著提高,能够支持2nm及以下的制程,但其成本和复杂性也将成倍增加。

- 超越光刻的新技术: 当传统光学光刻的物理和经济成本高到无法承受时,行业需要探索全新的路径。

- 纳米压印技术: 如前所述,精度高,但量产良率和成本是巨大挑战。

- 定向自组装: 让两块“亲水”和“疏水”的聚合物在引导下自动排列成周期性图案,可用于制造DRAM或某些特定结构的芯片。

- 电子束直写: 用电子束直接“画”出图案,精度极高,但速度极慢,主要用于制造光刻掩模版或小批量、高价值的芯片。

- 3D集成: 当2D平面上的晶体管尺寸缩放遇到瓶颈时,向空间发展是必然趋势,将不同功能的芯片堆叠在一起(Chiplet技术),或在硅片内部垂直堆叠晶体管(3D NAND),这需要新的光刻和刻蚀技术来处理三维结构。

- 计算光刻与AI: 随着多重曝光和复杂工艺的增加,光刻过程变得异常复杂,利用人工智能和机器学习来优化OPC算法、预测和修复缺陷、提高良率,变得越来越重要。

微纳米芯片技术和光刻技术是相辅相成、共同演进的。

- 微纳米芯片技术的目标是追求更高的性能、更低的功耗和更强的功能,其驱动力是摩尔定律。

- 光刻技术是实现这一目标的核心工具,它通过不断挑战光的物理极限,将工程师设计的蓝图变为现实。

从g-line到EUV,从单次曝光到多重曝光,再到探索高NA-EUV和全新的制造范式,光刻技术的每一次突破都标志着人类在微观世界迈出的坚实一步,这场“微观雕刻”的竞赛还将继续,光刻技术将继续作为半导体产业的基石,驱动着整个信息社会的进步。