FPGA音频采集技术是一种基于现场可编程门阵列(FPGA)实现的音频信号数字化处理方案,通过硬件级并行处理和可重构特性,在低延迟、高实时性和灵活配置方面展现出显著优势,该技术结合了模数转换(ADC)、数字信号处理(DSP)和数据传输接口,广泛应用于音频设备、工业控制、医疗仪器及消费电子等领域,以下从系统架构、关键技术、实现流程及优势分析等方面展开详细阐述。

系统架构与核心模块

FPGA音频采集系统的典型架构包括前端模拟电路、ADC模块、FPGA处理单元及数据输出接口,前端模拟电路负责麦克风或线路输入信号的调理,包括放大、滤波和偏置调整,确保信号幅度匹配ADC输入范围,ADC模块将模拟音频信号转换为数字信号,常用分辨率包括16bit、24bit和32bit,采样率覆盖8kHz至192kHz,以满足不同应用需求,FPGA作为核心处理单元,实现数据缓存、滤波、混音、格式转换等功能,并通过SPI、I2S、UART或USB等接口将处理后的音频数据传输至上位机或存储设备。

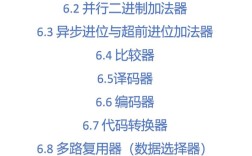

关键技术实现

-

ADC控制与数据采集

FPGA通过配置ADC的控制寄存器(如采样率、增益等),启动转换过程并读取数字音频数据,以I2S接口为例,FPGA需生成LRCK(左右声道时钟)、BCLK(位时钟)和SDATA(串行数据)信号,确保数据与时钟同步,对于48kHz采样率、24bit分辨率的音频,BCLK频率为48kHz×24×2=2.304MHz,FPGA需精确生成该时钟并完成数据解包。 -

数字信号处理

FPGA内部通过硬件描述语言(Verilog/VHDL)实现DSP算法,常见功能包括:- FIR滤波:用于抗混叠滤波或带通滤波,采用乘法累加(MAC)单元并行计算,滤波器系数可通过外部配置动态加载。

- 音频效果处理:如混响、均衡(EQ)等,通过延迟线和卷积运算实现,延迟线深度由FPGA内部BRAM资源决定。

- 噪声抑制:采用谱减法或自适应滤波算法,实时消除环境噪声。

以FIR滤波为例,假设滤波器阶数为32,每个采样周期需完成32次乘法和31次加法,FPGA可通过流水线技术将运算拆分为多个阶段,单时钟周期即可完成一次滤波,显著提升处理效率。

(图片来源网络,侵删)

(图片来源网络,侵删) -

数据缓存与传输

FPGA内部采用双端口RAM(DPRAM)或FIFO缓存音频数据,实现数据采集与传输的异步处理,当ADC采样率为48kHz时,每秒产生96KB数据(16bit立体声),FIFO需具备足够深度(如4KB)以防止数据溢出,对于USB传输接口,FPGA需实现USB协议栈,将音频数据打包为UAC(USB Audio Class)格式,支持即插即用。 -

低功耗与实时性优化

通过动态时钟门控和部分重构技术,FPGA可在非活跃模块关闭时钟以降低功耗,实时性方面,FPGA的硬件并行特性确保音频处理延迟可控制在微秒级,相比软件处理(毫秒级)优势显著。

典型应用场景

- 专业音频设备:如数字调音台,利用FPGA实现多通道音频实时混音和效果处理,延迟低于1ms。

- 语音交互系统:在智能音箱或车载语音中,FPGA完成语音活动检测(VAD)和降噪,提升识别准确率。

- 医疗仪器:如助听器,通过FPGA实现自适应增益控制和反馈抑制,优化听力补偿效果。

技术挑战与解决方案

| 挑战 | 解决方案 |

|---|---|

| 高精度ADC同步 | 采用FPGA全局时钟(Global Clock)和PLL锁相环,确保多ADC采样严格同步。 |

| 资源限制 | 优化算法结构,如用分布式乘法器替代专用DSP块,或采用外部DRAM扩展存储。 |

| 电磁兼容性(EMC) | 在PCB布局中隔离模拟与数字地,添加磁珠滤波和屏蔽层。 |

相关问答FAQs

Q1:FPGA与DSP在音频采集中的性能差异如何?

A1:FPGA采用硬件并行架构,适合低延迟、高并发的实时处理(如多通道音频混音),而DSP通过软件编程实现灵活性,适合复杂算法迭代,FPGA的延迟可稳定在微秒级,但开发难度较高;DSP开发周期短,但延迟通常为毫秒级,在32通道音频采集系统中,FPGA可同时处理所有通道的数据,而DSP需分时复用,可能导致资源瓶颈。

Q2:如何选择FPGA的型号用于音频采集系统?

A2:选择需考虑以下因素:

- 逻辑资源:中等规模(如Lattice ECP5或Xilinx Artix-7)可满足单通道至8通道处理需求;

- DSP slices:每通道24bit FIR滤波需约10-20个DSP48E(Xilinx),需根据算法复杂度预留余量;

- I/O数量:支持多路I2S、SPI及高速接口(如USB 3.0),如Xilinx Zynq系列集成了ARM核,便于嵌入式系统集成。

需评估开发工具链(如Vivado、Quartus)和成本,工业级应用推荐耐高低温的FPGA型号(如-40℃至85℃工作温度)。