DRAM作为现代计算系统的核心存储部件,其性能、容量和成本直接决定了电子设备的能力边界,DRAM的发展始终面临着一系列难以突破的技术瓶颈,这些瓶颈不仅限制了技术的迭代速度,也对产业链提出了严峻挑战,最关键的技术瓶颈主要集中在物理极限逼近、工艺复杂性提升、良率控制以及新兴技术替代风险四个维度。

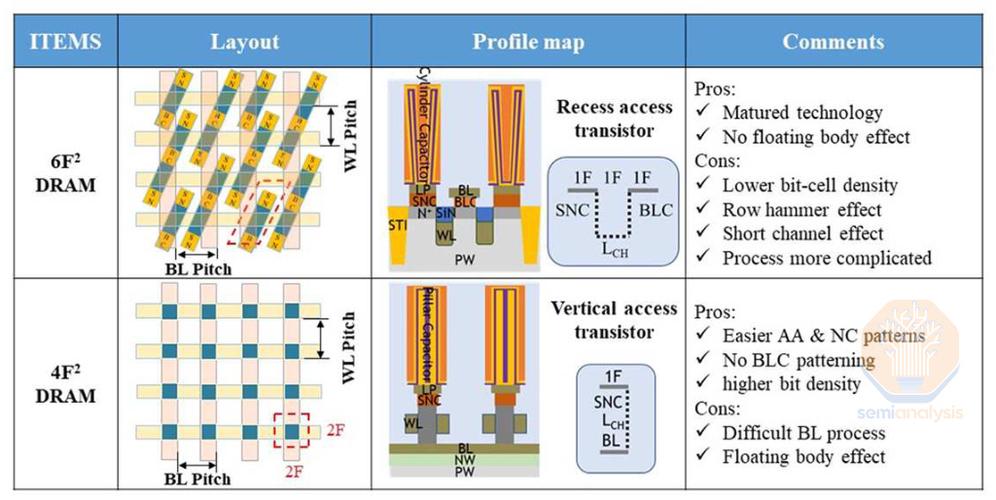

从物理极限的角度来看,DRAM的核心存储单元由一个晶体管和一个电容构成(1T1C结构),随着制程节点不断微缩,电容的存储面积急剧减小,导致电荷保持能力大幅下降,电容作为存储电荷的关键元件,其容量与面积成正比,当制程从10nm级别迈向7nm、5nm甚至更先进节点时,电容的物理尺寸已接近原子级别,进一步缩小空间极为有限,为了维持足够的电荷量,工程师不得不通过增加电容的三维结构(如深沟槽电容)来弥补平面面积的不足,但这会显著增加工艺难度和制造成本,晶体管的漏电流问题也日益突出,当栅极厚度缩减至几个原子层时,量子隧穿效应会导致电荷泄露,不仅增加功耗,还可能引发数据错误,根据国际半导体技术路线图(ITRS)的预测,DRAM的物理极限将在2nm节点左右显现,届时传统结构可能无法满足基本的存储需求。

工艺复杂性的提升是另一个难以逾越的瓶颈,为了突破物理限制,DRAM制造商不断引入新的材料和结构,例如用高k金属栅极替代多晶硅栅极,用钴或钌等低电阻金属替代传统的铜互连,以及采用多重曝光技术来提升光刻精度,这些新技术的引入虽然在一定程度上缓解了缩放难题,但也带来了工艺步骤的指数级增长,以多重曝光为例,当单次曝光无法满足分辨率要求时,需要多次套刻曝光,这不仅增加了生产时间,还提高了对准误差的风险,DRAM的晶圆尺寸已从300mm转向450mm,以降低单位成本,但更大的晶圆对工艺均匀性和缺陷控制提出了更高要求,根据行业数据,先进DRAM制程的工艺复杂度较十年前提升了3倍以上,而生产线的投资成本也从数十亿美元跃升至百亿美元级别,这使得新进入者几乎无法承受,进一步加剧了市场垄断。

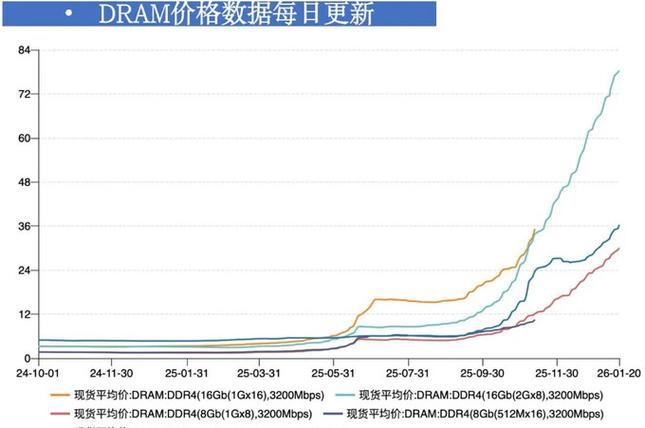

良率控制是制约DRAM产能和成本的核心问题,随着制程节点微缩和结构复杂化,晶圆制造过程中的缺陷密度显著增加,深沟槽电容的刻蚀工艺需要极高的均匀性,任何微小的偏差都可能导致电容性能差异;而多层互连中的金属沉积和化学机械抛光(CMP)步骤,如果厚度控制不当,可能引发短路或断路,据行业统计,10nm以下DRAM制程的良率比20nm制程低15-20个百分点,这意味着每生产一批晶圆,将有大量芯片因缺陷而报废,为了提升良率,制造商需要投入巨额资金进行工艺优化和缺陷检测,例如采用人工智能算法分析生产数据,或引入更先进的电子显微镜进行实时监控,良率的提升并非线性,当良率超过90%后,每提高1个百分点都需要数倍的努力和成本,这直接推高了DRAM的最终售价,形成了“技术先进-成本高昂-良率压力-成本更高”的恶性循环。

新兴存储技术的潜在替代风险也对DRAM构成了长期挑战,随着人工智能、大数据和物联网的快速发展,市场对存储器的需求不再局限于高速度,而是更倾向于高带宽、低功耗和非易失性等特性,这使得DRAM在部分应用场景下面临竞争压力,3D XPoint技术试图通过存储级内存(SCM)填补DRAM和NAND之间的性能空白;ReRAM、MRAM等阻变存储器凭借接近DRAM的读写速度和非易失性特性,在边缘计算领域展现出潜力;而光子存储技术则可能从根本上改变数据存储的物理原理,虽然这些技术目前尚无法在性能和成本上全面挑战DRAM,但其快速发展可能在未来5-10年内重塑存储市场格局,迫使DRAM厂商加速技术迭代,否则可能面临被边缘化的风险。

| 瓶颈维度 | 核心问题 | 技术挑战 | 影响程度 |

|---|---|---|---|

| 物理极限 | 电荷存储能力下降、漏电流增加 | 电容三维化、原子级栅极控制 | 极高 |

| 工艺复杂性 | 多重曝光、新材料引入 | 工艺步骤增加、对准精度要求提升 | 高 |

| 良率控制 | 缺陷密度增加、均匀性要求高 | 检测成本上升、优化难度加大 | 高 |

| 新兴技术替代 | 非易失性存储器竞争 | 性能替代、市场分流 | 中长期 |

DRAM的技术瓶颈是多重因素交织的结果,既有物理规律的限制,也有工艺和成本的制约,同时还面临外部技术的竞争压力,要突破这些瓶颈,不仅需要材料科学、光刻技术和封装工艺的革命性创新,还需要产业链上下游的协同合作,以及新型计算架构的适配调整,DRAM的发展路径可能不再是单纯的制程微缩,而是通过异构集成、3D堆叠和混合存储等技术,在特定场景下实现性能与成本的平衡,以应对日益复杂的计算需求。

相关问答FAQs:

Q1:为什么DRAM的制程微缩比CPU更困难?

A1:DRAM的1T1C结构对存储密度和电荷保持能力要求极高,其核心瓶颈在于电容的缩放,当制程微缩时,电容面积急剧减小,即使采用三维结构(如深沟槽电容),也难以弥补电荷存储量的损失,相比之下,CPU主要通过晶体管数量的增加和性能提升来优化,其缩放难度相对较低,DRAM对工艺均匀性和缺陷容错率的要求更严格,良率控制难度更大,这进一步限制了其制程微缩的速度。

Q2:3D堆叠技术能否完全解决DRAM的物理瓶颈?

A2:3D堆叠技术(如高带宽存储器HBM)通过在垂直方向上集成多层DRAM芯片,显著提升了带宽和存储密度,能够在一定程度上缓解平面缩放的压力,它无法完全解决物理瓶颈:堆叠层数的增加会带来散热和信号延迟问题,需要通过TSV(硅通孔)和先进封装技术解决;电容的物理缩放极限依然存在,3D堆叠只是“横向转纵向”的折中方案,而非根本性突破,3D堆叠是重要的技术路径,但仍需结合新材料和新结构(如MRAM混合集成)才能应对长期挑战。