数字集成电路设计与技术:从概念到芯片的完整旅程

数字集成电路设计与技术是一个多学科交叉的领域,它结合了电子工程、计算机科学和物理学,旨在将抽象的算法和功能需求,转化为可以在硅片上物理实现的、能够高效运行的电子电路,这个过程复杂而精密,是现代信息社会的基石。

第一部分:核心基础概念

在深入了解设计流程之前,必须理解几个核心概念:

-

数字信号与模拟信号

- 数字信号:在离散的时间点上取有限个值的信号,在数字IC中,通常用高电平(代表逻辑'1')和低电平(代表逻辑'0')来表示,这种表示方式对噪声不敏感,易于存储和处理。

- 模拟信号:在连续时间上可以取任意值的信号,现实世界中的大多数信号(如声音、温度、光线)都是模拟信号。

-

晶体管:构建数字世界的积木

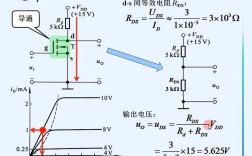

- 现代数字IC的基础是MOSFET(金属-氧化物-半导体场效应晶体管),它可以被看作一个电子开关。

- 通过控制栅极的电压,可以决定源极和漏极之间是否导通(开关闭合,代表'1')或截止(开关断开,代表'0')。

- 数以亿计的晶体管通过复杂的互连方式,构成了实现各种逻辑功能的门电路(如与门、或门、非门等)。

-

设计抽象层次 这是现代IC设计的核心思想,即“分而治之”,将一个复杂的系统分解成不同层次的抽象,每一层只关注特定的功能,而隐藏底层细节。

(图片来源网络,侵删)

(图片来源网络,侵删)层次 描述 示例 系统级 定义整个芯片的功能、性能和接口。 “设计一个支持5G通信的基带处理器。” 算法/行为级 用编程语言(如C/C++/SystemC)描述算法和数据处理流程。 实现一个FFT(快速傅里叶变换)的算法代码。 RTL级 (Register-Transfer Level) 数字设计的核心层次,描述数据在寄存器之间的流动和变换。 Verilog或VHDL代码,描述模块、状态机、组合/时序逻辑。 逻辑门级 将RTL代码转换为基本的逻辑门(与、或、非等)和触发器。 AND2, OR2, DFF等标准单元库中的元件。 电路/晶体管级 用晶体管和互连线来设计逻辑门和基本单元。 用CMOS晶体管搭建一个NAND2门。 物理版图/几何级 芯片制造的最终数据,定义了硅片上每一层(多晶硅、金属、有源区等)的精确几何形状和位置。 GDSII文件,包含所有用于光刻的图形信息。

第二部分:数字IC设计流程

一个典型的数字IC设计流程遵循从上到下的方法,并包含多次验证和迭代。

前端设计

-

规格定义

- 明确芯片的功能、性能(如工作频率)、功耗、面积、成本等目标。

- 这是整个项目的基石,后续所有设计都围绕它展开。

-

架构设计与建模

- 在系统级和算法级进行设计,确定芯片的总体架构(如CPU核、DSP、内存、总线如何组织)。

- 使用SystemC/C++进行建模和仿真,快速评估不同架构方案的优劣。

-

RTL设计与编码

(图片来源网络,侵删)

(图片来源网络,侵删)- 这是将架构设计转化为具体可实现的代码的关键步骤。

- 工程师使用硬件描述语言,主要是Verilog和VHDL,在RTL级描述电路的行为。

- 关键原则:代码必须是可综合的,即能被EDA工具自动转换为逻辑门电路。

-

功能验证

- 目的:确保RTL代码的功能与设计规格完全一致,是整个设计流程中最耗时、最关键的环节。

- 方法:

- 仿真:使用测试激励驱动RTL代码,检查输出结果是否正确,主流工具有Cadence Xcelium, Synopsys VCS。

- 形式验证:通过数学方法证明两个设计版本(如RTL和门级)在功能上等价,或证明某段代码不存在某种bug,速度快,但覆盖率有限。

后端设计

-

逻辑综合

- 目的:将RTL代码自动转换为由标准单元库中的逻辑门和触发器构成的网表。

- 过程:综合工具(如Synopsys Design Compiler)会根据时序、功耗、面积的约束,进行优化,生成一个门级网表文件(通常是EDIF格式)。

-

物理设计

- 这是将逻辑网表转化为物理版图的过程,非常复杂。

- a. 布局:将数十万到数百万个标准单元合理地放置在芯片的“核心区域”。

- b. 布线:在已经放置好的单元之间,按照设计规则,连接金属线,形成电路。

- c. 时序分析:在整个布局布线过程中,必须不断分析信号从源端到目的端的传播延迟,确保所有路径都能在时钟周期内完成操作,这是保证芯片能跑到预期频率的关键。

- d. 功耗分析:分析芯片的静态功耗和动态功耗,并进行优化。

- e. 可测性设计:在芯片中插入专门的测试电路(如扫描链),以便在制造后能快速、有效地测试芯片是否存在制造缺陷。

- 主要工具:Cadence Innovus, Synopsys IC Compiler。

-

物理验证

- 在版图完成后,必须进行一系列检查,确保版图是正确和可制造的。

- 设计规则检查:检查版图的几何尺寸是否符合代工厂的制造工艺要求。

- 版图原理图对比:将提取出的版图电路网表与综合后的逻辑网表进行对比,确保两者在电气功能上完全一致。

- 天线效应检查:检查长金属线在制造过程中可能积累的电荷是否会击穿晶体管。

制造与封测

-

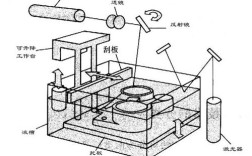

制造

- 将最终的GDSII文件提交给代工厂,如台积电、三星、中芯国际。

- 通过光刻、刻蚀、离子注入、薄膜沉积等一系列复杂的半导体工艺,在硅晶圆上制造出成千上万个芯片。

-

封装与测试

- 封装:将单个芯片从晶圆上切割下来,用外壳和引线框架保护起来,并连接到外部引脚。

- 测试:对封装好的芯片进行全面的测试,筛选出有缺陷的芯片,并确保良品的功能和性能都符合规格。

第三部分:关键技术趋势

-

摩尔定律的延续与挑战

- 摩尔定律(集成度每18-24个月翻一番)正在逼近物理和经济的极限。

- 延续方法:

- 先进工艺节点:从7nm, 5nm, 3nm向更小尺寸迈进。

- 晶体管结构创新:如FinFET(鳍式场效应晶体管)和GAAFET(全环绕栅极晶体管),用于更好地控制短沟道效应。

- 先进封装技术:如Chiplet(芯粒),将不同功能的小芯片封装在一起,而非单颗SoC,以降低成本和风险。

-

低功耗设计

- 移动设备和数据中心对功耗要求极高。

- 技术:电源门控、时钟门控、多电压域、动态电压与频率调节等。

-

验证的挑战

- 随着设计规模增大,验证的复杂度呈指数级增长。

- 趋势:从传统的仿真转向形式验证、UVM(通用验证方法学)和硬件加速器/仿真器。

-

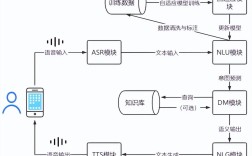

面向特定领域的架构

- 通用处理器(如CPU)已无法满足AI、5G等特定领域的性能需求。

- 趋势:设计ASIC和SoC,集成NPU(神经网络处理单元)、DPU(数据包处理单元)等专用硬件加速器。