这不仅仅是一个技术名词,它代表了现代无线通信系统设计的一个核心理念和未来方向,下面我将从基本概念、核心理论、关键技术、挑战与优势、以及应用与发展等多个维度,为您进行深入且全面的解析。

什么是全数字接收机?

我们需要理解它与传统的模拟/数字混合接收机的区别。

传统接收机(模拟前端 + 数字后端)

这是几十年来通信设备的主流架构,其工作流程如下:

- 天线接收:接收到微弱的射频信号。

- 低噪声放大:通过LNA将信号放大,同时尽量不引入额外噪声。

- 混频:通过混频器将高频的射频信号下变频到较低的中频或基带信号。

- 滤波:使用模拟滤波器滤除带外干扰和噪声。

- 模数转换:使用ADC将模拟信号转换为数字信号。

- 数字处理:在数字域进行后续的解调、解码等处理。

核心特点:

- “模拟为主,数字为辅”:射频前端(LNA, 混频器, 滤波器等)占据主导地位,完成最关键的信号处理。

- 性能瓶颈:系统的性能(如灵敏度、线性度)主要由模拟前端的元器件性能决定,而这些元器件(如高性能ADC、模拟滤波器)往往成本高、功耗大、难以集成。

- 灵活性差:一旦硬件设计完成,接收机的频率、带宽、调制方式等就固定了,难以通过软件升级来支持新的标准。

全数字接收机

全数字接收机的核心理念是:尽可能将信号处理向数字域迁移,将ADC尽可能靠近天线,甚至直接放在天线之后,其工作流程如下:

- 天线接收:接收到射频信号。

- 滤波与放大:可能只保留一个简单的带通滤波器和LNA用于保护天线和提供初步增益。

- 直接射频采样:使用一个高速、高分辨率的ADC,直接对射频信号进行采样,将其转换为数字信号。

- 数字下变频:在数字域完成混频、滤波、抽取等所有本应由模拟前端完成的任务。

- 数字信号处理:进行后续的解调、解码、同步等处理。

核心特点:

- “数字为主,模拟为辅”:将复杂的模拟信号处理任务用灵活的数字算法来实现。

- 软件定义:接收机的几乎所有功能(频率、带宽、调制方式、波形设计等)都可以通过软件编程来定义和重构。

- 高度集成:核心功能在数字芯片(如FPGA, ASIC)上实现,有利于实现片上系统,大幅减小体积、重量和功耗。

核心理论与挑战

全数字接收机并非简单地将模拟部分替换掉,它背后有一套深刻的理论支撑,并面临着一系列严峻的技术挑战。

核心理论

- 奈奎斯特采样定理:这是ADC采样的基石,为了无失真地恢复原始信号,采样率必须至少是信号最高频率的两倍($fs \ge 2f{max}$),在射频采样场景下,这意味着ADC需要工作在GHz级别,这是全数字接收机面临的首要挑战。

- 带通采样定理:对于中心频率为$f_c$、带宽为B的射频信号,只要采样率$f_s$满足 $2B \le f_s \le \frac{2f_c}{n-1}$ (其中n为正整数,且 $f_c$落在 $n \cdot \frac{f_s}{2}$ 和 $(n+1) \cdot \frac{f_s}{2}$ 之间),就可以通过采样将信号搬移到基带或低中频,这为直接射频采样提供了理论依据,降低了对ADC采样率的要求。

- 数字下变频:这是全数字接收机的“数字心脏”,它主要包括:

- 数字混频:用数字本振(NCO,Numerically Controlled Oscillator)与ADC输出的信号相乘。

- 滤波:使用FIR(有限冲激响应)或IIR(无限冲激响应)滤波器进行低通滤波,滤除混频产生的高频分量。

- 抽取:在降低数据速率的同时,防止混叠,通常与滤波器结合,实现高效的CIC(积分梳状)滤波器或半带滤波器。

- 数字锁相环:用于载波同步和时钟同步,其性能直接影响解调的准确性。

关键技术挑战

全数字接收机的实现难度远高于传统接收机,挑战主要集中在ADC和数字信号处理算法上。

| 挑战领域 | 具体问题 | 技术难点 |

|---|---|---|

| 模数转换器 | 采样率 | 射频信号频率很高(GHz级),要求ADC具备极高的采样率,目前技术极限在Gsps级别。 |

| 带宽 | ADC的模拟输入带宽必须能覆盖整个射频信号带宽,否则信号失真。 | |

| 分辨率 | 微弱的射频信号要求ADC有足够的位数(如12-16位)来保证信噪比,但高分辨率和高采样率通常是矛盾的。 | |

| 功耗与成本 | 高性能ADC是全数字接收机中最昂贵、功耗最高的器件之一。 | |

| 数字信号处理 | 处理能力 | 直接处理GHz级的数字流,对FPGA或ASIC的计算能力、存储带宽要求极高,带来巨大的功耗和面积开销。 |

| 算法复杂度 | 数字下变频、滤波、同步等算法需要在极低的功耗下实时运行,算法优化至关重要。 | |

| 射频前端 | 抗干扰 | 将ADC提前,意味着模拟滤波环节减少,射频前端的带外干扰会直接进入ADC,可能导致ADC饱和或失真,需要更强大的数字抗干扰算法。 |

| 驱动能力 | 高速ADC需要前端提供特定的输入阻抗匹配和驱动能力,对模拟电路设计提出了新要求。 |

关键技术模块详解

-

高分辨率、宽带宽ADC

(图片来源网络,侵删)

(图片来源网络,侵删)- 作用:是全数字接收机的“眼睛”,其性能直接决定了接收机的动态范围和灵敏度。

- 技术方向:采用多比特量化、过采样、噪声整形等技术(如Σ-Δ ADC)来提升性能。

-

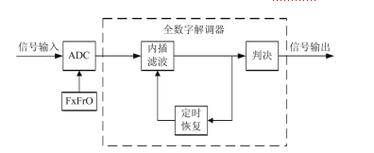

数字下变频器

- 作用:将射频/中频数字信号搬移到基带,并滤除无用分量,降低数据速率。

- 实现方式:通常在FPGA中通过硬件描述语言实现,包含NCO、乘法器、滤波器和抽取器。

-

数字滤波器

- 作用:用于信道选择、抗混叠、成形滤波等。

- 类型:FIR滤波器因其稳定性好、线性相位特性,成为主流选择,CIC滤波器因其无需乘法器,常用于多级抽取的第一级。

-

数字本振与频率合成器

- 作用:产生高精度、高纯度的正交本振信号(I/Q路),用于混频。

- 实现方式:基于NCO和相位累加器,其频率分辨率和杂散抑制是关键指标。

-

数字锁相环 与载波/定时同步

- 作用:跟踪接收信号的载波频率和相位偏移,以及时钟定时误差,是相干解调的前提。

- 实现方式:通过鉴相器、环路滤波器和数字压控振荡器构成的反馈环路,在数字域完成同步。

优势与应用

尽管挑战巨大,但全数字接收机的优势是革命性的,使其成为5G/6G、卫星通信、雷达等前沿领域的必然选择。

主要优势

- 极高的灵活性:软件定义无线电的核心,同一套硬件平台,只需更新软件,即可支持不同的通信标准(如4G/5G/Wi-Fi/蓝牙),甚至支持多种标准并行或动态切换。

- 更优的性能:

- 高线性度:数字处理没有非线性失真,动态范围远超模拟电路。

- 高一致性:数字芯片批量生产的一致性极佳,避免了模拟元器件的参数漂移问题。

- 易于校准:可以通过数字算法对系统进行精确的校准,补偿模拟前端的幅相误差、频率偏移等。

- 小型化、低功耗、低成本:

- 高度集成:将大量模拟电路功能集成到单个数字芯片上,减小了PCB面积、组件数量和系统体积。

- 批量生产:数字芯片的制造成本随着规模迅速下降,长期来看更具成本优势。

- 快速升级与演进:新协议、