CD4052是一款由Texas Instruments(原RCA)设计的模拟多路复用/解复用器,属于CMOS工艺的4000系列集成电路,该器件具有双4通道模拟开关功能,能够在数字信号控制下实现多路模拟信号的选择与切换,广泛应用于数据采集系统、信号路由、测试设备等领域,以下从技术特性、引脚功能、工作原理、典型应用及注意事项等方面进行详细说明。

技术特性

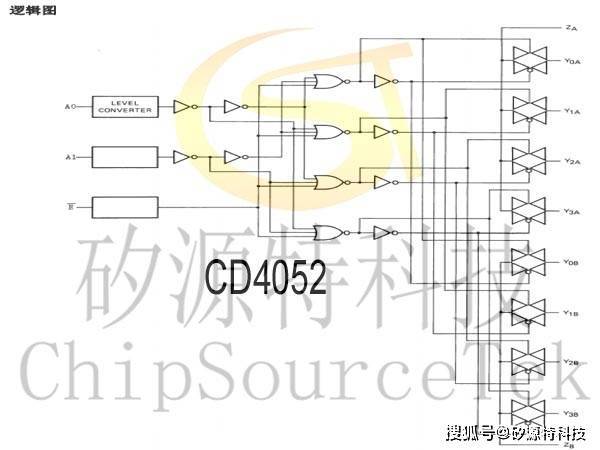

CD4052的核心功能是通过2位数字地址线(A0、A1)选择4组独立的模拟开关通道,每组开关包含一个常开端(Y0-Y3)、一个常闭端(Z0-Z3)以及一个公共端(X),其主要技术参数包括:

- 电源电压范围:3V至18V,兼容TTL/CMOS逻辑电平。

- 开关特性:

- 导通电阻(Ron):典型值为125Ω(VDD=15V,VSS=0V),随电源电压降低而增大。

- 带宽(-3dB):约40MHz(Ron×Cload=1kΩ×10pF时)。

- 通道串扰:-50dB(1MHz信号)。

- 逻辑兼容性:输入控制端(A0、A1、INH)可直接与CMOS或TTL电路连接,INH为高电平时禁止所有通道切换。

- 封装形式:DIP-16、SOIC-16、TSSOP-16等,便于不同场景的PCB布局。

引脚功能

CD4052采用16引脚封装,各引脚定义如下表所示:

| 引脚编号 | 名称 | 功能说明 |

|---|---|---|

| 1-4 | Y0-Y3 | 常开端,分别对应4个通道的输出引脚 |

| 5-8 | Z0-Z3 | 常闭端,分别对应4个通道的输入引脚 |

| 9 | INH | 禁止端,高电平时所有通道断开,低电平时允许地址切换 |

| 10 | A0 | 地址线0,与A1组合选择通道(00=通道0,01=通道1,10=通道2,11=通道3) |

| 11 | A1 | 地址线1,功能同上 |

| 12 | X | 公共端,作为所有通道的共用输入或输出端 |

| 13-16 | VDD-VSS | 电源引脚,VDD接正电源,VSS接地(GND) |

工作原理

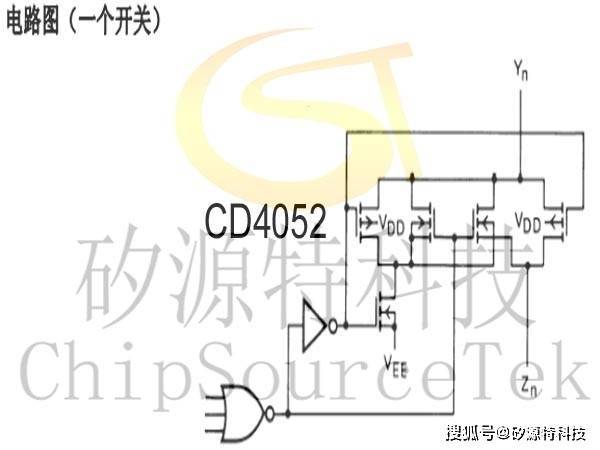

CD4052的内部结构由两组4通道模拟开关组成,每组开关由CMOS传输门构成,通过地址译码器控制通道选择,当INH为低电平时,A0和A1的4种组合分别对应连接X与Y0-Y3(常开)或X与Z0-Z3(常闭)。

- A0=0、A1=0:X与Y0导通,X与Z0断开;

- A0=1、A1=0:X与Y1导通,X与Z1断开。

信号流向可根据设计需求灵活配置,例如将X作为输入端,Y0-Y3作为输出端实现4选1多路复用;或将X作为输出端,Z0-Z3作为输入端实现4选1解复用,需要注意的是,模拟信号的幅值需满足VSS≤Vin≤VDD,否则可能导致开关性能下降或损坏。

典型应用

- 多路数据采集系统:在ADC前端,通过CD4052切换多路传感器信号,分时输入ADC进行模数转换,减少ADC数量以降低成本。

- 音频信号切换:在音响设备中,用于切换不同音频源(如麦克风、线路输入)至功放输入端。

- 测试设备:在自动测试系统中,通过数字控制选择不同的测试信号或测量通道。

- 电平转换:利用其宽电源电压特性,实现不同电压域模拟信号的隔离传输。

设计注意事项

- 电源去耦:在VDD与VSS之间并联0.1μF陶瓷电容,以减少电源噪声对开关性能的影响。

- 信号幅度限制:输入信号峰值不得超过电源电压范围,避免闩锁效应(Latch-up)。

- 开关速度:高频应用时需考虑Ron和负载电容形成的RC时间常数,避免信号失真。

- 逻辑电平匹配:若控制端为TTL电平(VCC=5V),而CD4052使用15V电源,需确保INH、A0、A1的高电平不超过VDD,可通过分压电阻或电平转换电路实现。

相关问答FAQs

Q1:CD4052的导通电阻(Ron)是否受温度影响?

A1:是的,Ron具有正温度系数,温度每升高10℃,Ron约增加0.5%~1%,在精密应用中,需考虑温度变化对信号衰减的影响,或选择低温漂的替代型号(如ADG系列)。

Q2:如何抑制CD4052在切换通道时的瞬态干扰?

A2:可通过以下方法抑制干扰:①在公共端(X)和输出端(Y/Z)之间并联100pF~1nF滤波电容;②在地址切换端(A0/A1)增加RC滤波电路(如1kΩ电阻+100pF电容),避免快速跳变;③采用“先断后通”的软件延时策略,确保地址稳定后再切换通道。