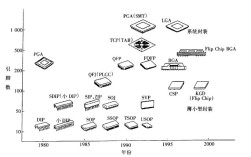

集成电路与FPGA技术的融合正在深刻重塑现代电子系统的设计范式,推动着从消费电子到工业控制、从人工智能到航空航天领域的革命性创新,集成电路(IC)作为将大量电子元件(如晶体管、电阻、电容等)集成在一小块半导体基片上的微型化电子器件,是现代信息技术产业的基石,而现场可编程门阵列(FPGA)作为一种半定制化集成电路,以其灵活性、可重构性和并行处理能力,成为连接通用处理器与专用集成电路(ASIC)的关键桥梁,两者的结合为解决复杂系统设计中的性能、功耗与成本矛盾提供了全新路径。

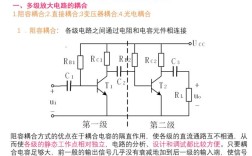

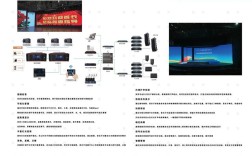

从技术本质来看,FPGA是在PAL、GAL等可编程器件基础上进一步发展的产物,其核心架构由可配置逻辑块(CLB)、输入输出单元(IOB)、布线资源(Routing Resources)和嵌入式存储器块(Block RAM)等组成,与ASIC的固定功能设计不同,FPGA允许用户通过硬件描述语言(HDL)如Verilog或VHDL进行逻辑设计,并通过现场烧写配置文件多次重构硬件电路,这种“软件定义硬件”的特性使其在原型验证、小批量生产及需要频繁升级的场景中具有独特优势,随着制程工艺的进步,现代FPGA已集成ARM硬核处理器、高速收发器、DSP模块和AI加速单元,形成“SoC+FPGA”的异构计算平台,例如Xilinx Zynq系列和Intel Cyclone 10 GX系列,可同时处理控制密集型与计算密集型任务,满足5G通信、边缘计算等应用的高性能需求。

在集成电路设计流程中,FPGA技术发挥着不可替代的作用,传统ASIC设计面临高昂的研发成本和漫长的流片周期(通常6-12个月),而FPGA原型验证可将设计风险提前暴露,通过快速迭代优化逻辑功能,将ASIC开发周期缩短30%-50%,以人工智能领域为例,神经网络模型的训练和推理需要极高的并行计算能力,GPU虽擅长并行处理,但功耗与灵活性受限;而FPGA通过定制化数据路径和流水线设计,可实现特定算法的硬件级加速,例如在图像识别中,FPGA能直接优化卷积运算的存储访问模式,降低延迟至毫秒级,同时功耗仅为GPU的1/3至1/2,FPGA在工业自动化中用于实时运动控制,其纳秒级中断响应能力远超通用处理器,可精准协调电机、传感器等多设备协同工作。

尽管优势显著,FPGA技术的普及仍面临挑战,FPGA的开发门槛较高,需要工程师具备硬件描述语言、数字电路设计和算法优化等多领域知识,而传统软件工程师向硬件开发转型的学习曲线陡峭;大规模FPGA的单元数量已达千万级,布线复杂度呈指数级增长,时序收敛成为设计难点,需依赖专业EDA工具(如Vivado、Quartus)进行综合与布局布线优化,FPGA的单位成本虽低于ASIC,但远高于MCU或DSP,在大批量应用中经济性不足,需通过设计复用和IP核共享降低开发成本。

随着Chiplet(芯粒)技术和3D封装的发展,FPGA将突破单芯片集成度的限制,通过多芯片互连实现更高性能的异构计算,AI辅助设计工具的兴起(如基于机器学习的自动布局布线算法)有望简化FPGA开发流程,使硬件设计像软件编程一样高效,在汽车电子领域,FPGA的实时处理能力和功能安全性(符合ISO 26262标准)使其成为自动驾驶感知系统的核心组件;在数据中心,FPGA加速卡可动态重构网络功能,支持5G/6G协议的灵活升级,这些趋势将进一步巩固FPGA在集成电路生态中的战略地位。

相关问答FAQs

Q1:FPGA与ASIC的主要区别是什么?如何选择?

A:FPGA是可重构的半定制化器件,支持多次编程,开发周期短、灵活性高,适合原型验证、小批量生产及需频繁迭代的应用;ASIC是全定制化器件,功能固定,性能和功耗最优,但研发成本高、周期长,适合大规模成熟产品(如手机处理器),选择时需综合考虑:若需求多变或需快速上市,选FPGA;若性能、功耗要求极致且产量大,选ASIC。

Q2:学习FPGA开发需要哪些基础知识?

A:需掌握数字电路逻辑(组合逻辑、时序逻辑)、硬件描述语言(Verilog/VHDL)、FPGA架构原理(CLB、RAM等模块)及开发工具(如Vivado、Quartus),建议先通过简单实验(如LED闪烁、计数器设计)熟悉流程,再学习IP核调用和时序约束优化,最后结合实际项目(如UART通信、图像处理算法加速)提升综合能力。