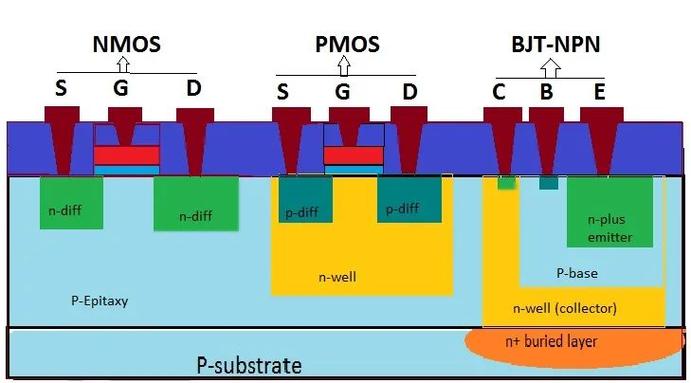

芯片CMOS工艺技术是现代半导体产业的基石,其发展水平直接决定了计算、通信、消费电子等领域的创新速度,CMOS(Complementary Metal-Oxide-Semiconductor,互补金属氧化物半导体)工艺的核心在于利用P型MOS(PMOS)和N型MOS(NMOS)晶体管的互补特性,构建低功耗、高集成度的逻辑电路,这一技术自1960年代诞生以来,便成为集成电路制造的主流选择。

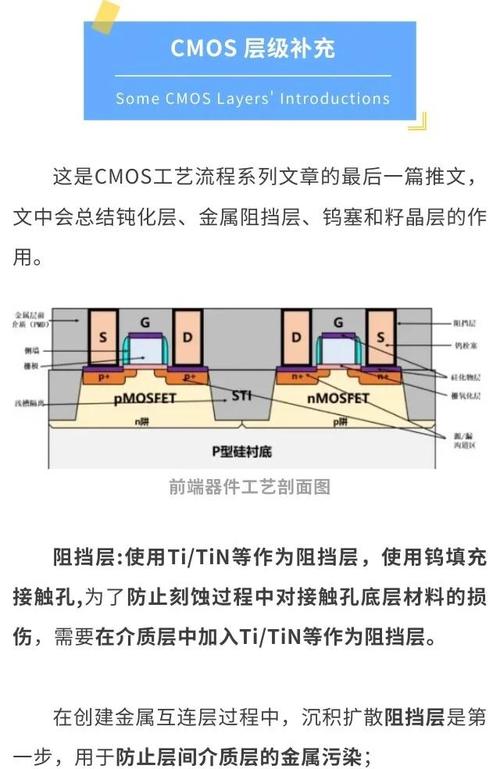

CMOS工艺技术的演进遵循摩尔定律的指引,通过不断缩小晶体管特征尺寸来提升芯片性能和集成度,从早期的10微米工艺发展到如今的3纳米、2纳米节点,工艺节点的缩小意味着在相同芯片面积上可容纳更多晶体管,同时开关速度更快、功耗更低,这一过程中,关键工艺环节不断突破:光刻技术从紫外光(UV)发展到深紫外光(DUV),再到极紫外光(EUV),使得更精细的电路图形得以实现;刻蚀技术从湿法刻蚀转向干法刻蚀,实现高深宽比结构的精确加工;薄膜沉积技术如化学气相沉积(CVD)和物理气相沉积(PVD)不断优化,确保晶体管各层薄膜的均匀性和厚度控制。

晶体管结构的创新是CMOS工艺发展的核心动力,当平面晶体管尺寸缩小至物理极限时,FinFET(鳍式场效应晶体管)应运而生,通过三维鳍状沟道结构增强栅极对沟道的控制能力,有效抑制漏电流,推动工艺进入14纳米及以下节点,近年来,GAA(Gate-All-Around,环绕栅)晶体管进一步取代FinFET,在纳米线或纳米片沟道周围实现全包围式栅极控制,电流控制能力更强,适用于3纳米及以下先进制程,晶体沟道材料也从传统的硅拓展到硅锗(SiGe)、二维材料(如二硫化钼)等,以应对短沟道效应带来的性能瓶颈。

CMOS工艺技术的多元化发展满足不同应用场景需求,逻辑工艺追求高性能与低功耗的平衡,如移动芯片采用低功耗(LP)工艺,服务器芯片采用高性能(HP)工艺;存储工艺如DRAM和NAND闪存通过堆叠技术(如3D NAND)提升容量;射频(RF)工艺和功率半导体工艺则针对无线通信和能源管理领域优化,整合高Q值电感、高压器件等特殊结构,先进封装技术如2.5D封装(硅中介层)和3D封装(TSV硅通孔)与CMOS工艺结合,实现芯片间的高密度互连,突破单芯片集成度的限制。

CMOS工艺技术也面临诸多挑战,随着节点进入亚纳米尺度,量子隧穿效应、散热问题、制造成本指数级上升等问题日益凸显,EUV光刻机的产能限制、先进材料的良率控制、以及设计-制造协同(Design-Technology Co-optimization, DTCO)的复杂性,都对产业发展提出更高要求,为应对这些挑战,行业正在探索光刻技术突破(如高NA EUV)、新材料体系(如碳纳米管、石墨烯)以及新型计算架构(如存算一体、神经形态芯片)。

相关问答FAQs:

-

问:CMOS工艺中的FinFET和GAA晶体管有何区别?

答:FinFET采用三维鳍状沟道,栅极仅在沟道两侧及顶部进行控制,而GAA晶体管的栅极完全包围沟道(如纳米线或纳米片),栅极控制面积更大,能有效抑制短沟道效应,适用于更先进的工艺节点(如3nm以下),提供更好的电流驱动能力和功耗控制。 -

问:为什么CMOS工艺成为芯片制造的主流技术?

答:CMOS工艺的核心优势在于其低静态功耗特性——PMOS和NMOS在静态时仅有一个管子导通,几乎不消耗功耗,CMOS电路具有噪声容限高、逻辑摆幅大、适合大规模集成等优点,能够满足现代芯片对性能、功耗和成本的综合需求,因此在逻辑、存储、射频等领域被广泛应用。