SOI技术的核心思想是在硅晶圆和顶层硅器件之间引入一层绝缘层(通常是二氧化硅,SiO₂),这个“硅-绝缘层-硅”的三明治结构,从根本上改变了传统体硅器件的特性,带来了诸多优势。

SOI技术主要分为两大主流路线,并在此基础上衍生出不同的实现方法:

两大主流SOI技术路线

根据顶层硅膜厚度的不同,SOI技术主要分为以下两类,它们服务于不同的应用场景。

薄膜全耗尽SOI - FD-SOI (Fully Depleted SOI)

这是目前移动和低功耗领域非常主流的技术,也是与FinFET竞争的关键技术之一。

-

核心特点:

(图片来源网络,侵删)

(图片来源网络,侵删)- 极薄的顶层硅膜:通常在几纳米到几十纳米的量级。

- 全耗尽:在正常工作电压下,栅极电场可以完全穿透整个薄的顶层硅膜,耗尽层中所有的自由载流子(电子或空穴)。

-

工作原理与优势:

- 卓越的短沟道效应抑制能力:由于硅膜极薄,沟道被栅极“紧紧包裹”,漏电被大大抑制,这使得FD-SOI可以在比传统体硅更小的尺寸下稳定工作,漏电极低。

- 低功耗:

- 静态功耗极低:出色的短沟道控制能力意味着漏电流极小,这在待机状态下至关重要。

- 动态功耗更低:由于体硅和源漏区之间被绝缘层隔离,没有体效应引起的寄生电容,开关速度更快,动态功耗更低。

- 高驱动电流:全耗尽状态下的沟道中载流子迁移率更高,且可以轻松实现背栅极技术,进一步优化性能。

- 工艺简单且成本低:FD-SOI可以在成熟的体硅生产线上进行“迁移”,只需增加几道额外的掩膜和注入步骤,无需像FinFET那样引入复杂的3D结构,制造成本相对可控。

-

主要应用:

- 智能手机SoC:如意法半导体为三星、华为等高端手机提供的芯片。

- 物联网:对功耗极其敏感的设备。

- 汽车电子:需要高可靠性和低功耗的控制器。

- 射频应用:如RF-SOI,是手机射频前端模块的主流技术。

-

代表厂商:

- 意法半导体:FD-SOI技术的最大推动者和实践者,拥有全球领先的22nm FD-SOI和28nm FD-SOI工艺。

- 三星:也曾采用FD-SOI技术生产部分手机SoC。

厚膜部分耗尽SOI - PD-SOI (Partially Depleted SOI)

这是SOI技术早期的主要形式,至今仍在特定领域占据重要地位。

-

核心特点:

- 较厚的顶层硅膜:通常在100纳米以上。

- 部分耗尽:在正常工作电压下,栅极电场无法完全耗尽整个硅膜,硅膜的中心区域会保持中性,形成一个“浮体区”。

-

工作原理与优势:

- 高驱动电流:由于硅膜较厚,可以容纳更多的载流子,驱动电流能力更强,适合高性能应用。

- 闩锁效应免疫:绝缘层的存在彻底切断了体硅中寄生的PNPN结构,消除了CMOS电路中最致命的闩锁效应,大大提高了电路的可靠性。

- 集成度高:由于器件之间被绝缘层隔离,可以实现更密集的布线,寄生电容也更小。

- 抗辐射能力强:绝缘层可以有效阻挡高能粒子,减少其在硅中产生的电子-空穴对,从而降低单粒子翻转效应,这是其在航天领域备受青睐的关键原因。

-

主要应用:

- 航空航天与国防:抗辐射特性使其成为卫星、深空探测等领域的首选。

- 高压集成电路:如电源管理、汽车电子、智能功率模块等,绝缘层提供了天然的隔离,可以轻松实现高压器件与低压逻辑电路的单片集成。

- 图像传感器:背照式CMOS图像传感器中,BSI技术本身就要求移除底层硅,而SOI结构可以天然地实现这一点,提供更好的光吸收和串扰抑制。

-

代表厂商:

- Skyworks Solutions、Qorvo、Broadcom:这些射频领域的巨头广泛采用RF-SOI(一种PD-SOI)技术制造手机射频开关和滤波器。

- 意法半导体、英飞凌:在汽车和功率半导体领域有深厚的PD-SOI技术积累。

实现SOI晶圆的主流制造方法

无论是FD-SOI还是PD-SOI,其核心都是高质量的SOI晶圆,目前主流的制造方法有以下几种:

SIMOX (Separation by IMplantation of OXygen) - 氧离子注入法

- 原理:在标准的硅晶圆中,用高能氧离子注入机将高浓度的氧离子注入到晶圆表面下方的一定深度,然后在高温下(>1300°C)进行长时间退火,注入的氧离子与硅反应,在注入层下方形成一层连续的、均匀的二氧化硅(SiO₂)层,而注入层上方的硅则重结晶成为单晶硅层。

- 特点:技术成熟,可以制造高质量的SOI晶圆,是目前高端SOI晶圆(特别是用于射频和高压应用的)的重要方法之一,但设备昂贵,能耗高。

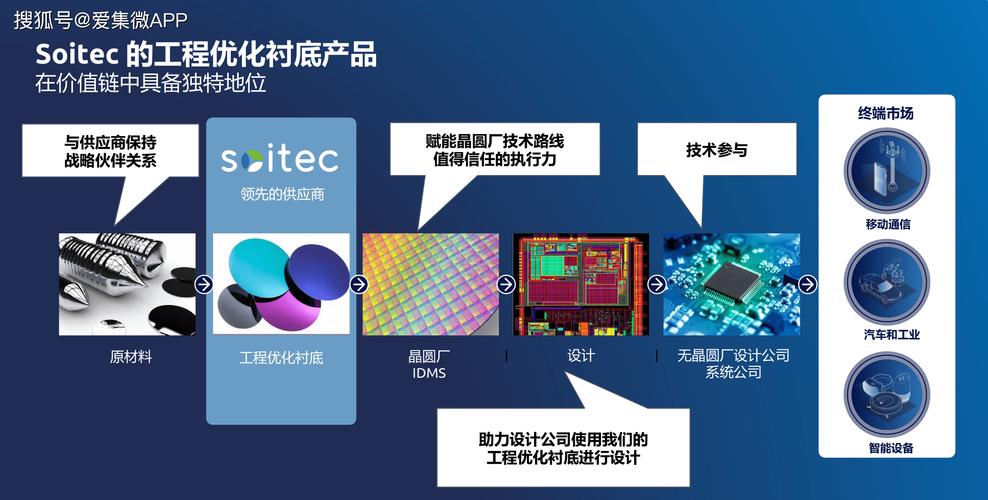

Smart Cut™ (智能剥离技术)

这是目前市场占有率最高、成本效益最好的方法,由法国Soitec公司开发并推广。

- 原理:

- 键合:首先将一块经过氢离子注入的“供体”硅晶圆和一块普通的“支撑”硅晶圆进行高温键合,使两块晶圆的表面紧密贴合。

- 剥离:在较低的温度下加热,氢离子在“供体”晶圆内部形成微弱的气泡层,使其沿着这个层精确地“撕开”或“剥离”。

- 修复:剥离后,“供体”晶圆上会留下一个极薄的硅膜,这个硅膜经过化学机械抛光和高温退火修复后,晶格质量得到恢复,形成高质量的顶层硅,而“支撑”晶圆下方则自然形成了绝缘的SiO₂层。

- 特点:

- 灵活性高:可以精确控制顶层硅膜的厚度(从几纳米到几百纳米)。

- 材料利用率高:一块昂贵的“供体”晶圆可以重复使用多次来制造多片SOI晶圆,成本远低于SIMOX。

- 质量好:顶层硅的晶格质量非常高,接近原始硅片。

- 可定制化:可以制造“绝缘层+硅+绝缘层”的三明治结构(如FD-SOI),或者在绝缘层上再生长其他材料,实现异质集成。

ELTRAN™ (Epitaxial Layer TRANSfer) - 外延层转移法

这是另一项由日本信越化学开发的SOI晶圆制造技术。

- 原理:

- 在一块牺牲晶圆上生长多孔硅层。

- 在多孔硅层上通过外延生长一层高质量的单晶硅。

- 将这块带有外延硅的晶圆与另一块支撑晶圆键合。

- 通过选择性地腐蚀掉多孔硅牺牲层,将外延硅层转移到支撑晶圆上。

- 特点:能够制造出顶层硅膜非常厚且质量极高的SOI晶圆,特别适合高压、大电流的功率器件应用。

SOI技术的未来发展趋势

- 与FinFET的共存与竞争:在7nm及以下节点,FinFET和FD-SOI是两条并行的技术路线,FinFET在极限性能上可能略有优势,而FD-SOI则在功耗、成本和设计便利性上表现出色,未来两者将在不同应用场景(如高性能计算vs.移动IoT)中继续竞争。

- 全环栅技术:当沟道宽度缩小到几个原子级别时,FinFET的“鳍”结构也难以有效控制沟道,GAA结构将成为下一代晶体管。FD-SOI平台是实现GAA技术的理想平台之一,因为其平面结构比FinFET的3D结构更容易在薄硅膜上堆叠多个栅极环绕沟道。

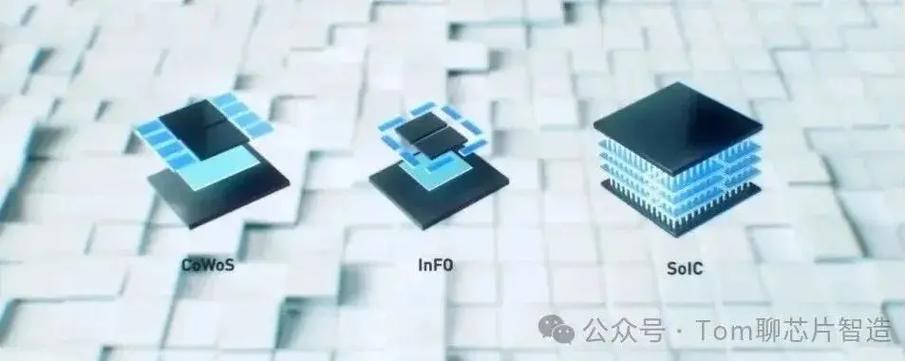

- 先进封装与异构集成:SOI技术的天然隔离特性使其非常适合与III-V族化合物半导体(如GaN、InP)、光子学器件等进行集成,实现“More than Moore”的异构集成,在单一封装内提供计算、通信、传感等多种功能。

- 面向特定应用的深化:

- 汽车:随着汽车智能化和电动化,对高可靠性、低功耗、高集成度的芯片需求激增,PD-SOI和FD-SOI都将迎来更大发展。

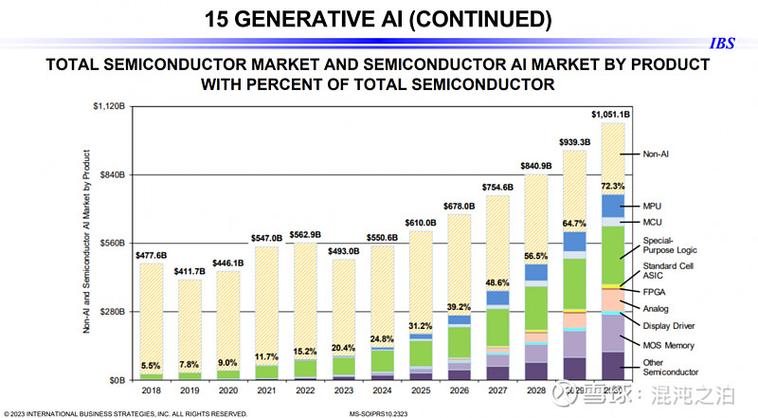

- AI/ML:AI推理芯片对能效比要求极高,FD-SOI的低功耗特性使其成为非常有竞争力的选择。

| 特性 | FD-SOI (薄膜全耗尽) | PD-SOI (厚膜部分耗尽) |

|---|---|---|

| 顶层硅膜厚度 | 极薄 (几nm - 几十nm) | 较厚 (>100nm) |

| 沟道状态 | 全耗尽 | 部分耗尽(存在浮体区) |

| 核心优势 | 极致的漏电控制、低功耗、高性能、成本适中 | 高驱动电流、闩锁效应免疫、抗辐射、适合高压 |

| 主要应用 | 智能手机SoC、IoT、低功耗芯片 | 射频开关、汽车电子、航空航天、功率IC、图像传感器 |

| 制造主流 | Smart Cut™ | Smart Cut™、SIMOX、ELTRAN™ |

SOI技术并非单一的技术,而是一个庞大的技术家族。FD-SOI凭借其出色的功耗性能和成本优势,在移动和物联网领域大放异彩;而PD-SOI则凭借其高可靠性和高功率处理能力,在射频、汽车和航天等“利基”市场占据不可替代的地位,随着Smart Cut™等制造技术的成熟和成本的降低,SOI技术的应用范围正在不断扩大,并在后摩尔时代扮演着越来越重要的角色。