硬件验证技术包括多种方法与工具,旨在确保硬件设计符合规格要求,在流片前发现并修复潜在缺陷,这些技术涵盖了从功能验证到性能分析,从仿真到形式化验证的多个维度,形成了完整的验证体系,以下从验证流程、核心方法、常用工具及发展趋势等方面详细阐述。

硬件验证的核心流程通常始于需求分析,明确设计规格与验证目标,随后制定验证计划,定义测试场景、覆盖指标及资源分配,在验证实施阶段,通过搭建验证环境、编写测试用例、运行仿真或形式化检查来验证设计功能,验证过程中发现的缺陷需反馈给设计团队进行修复,并通过回归测试确保修复未引入新问题,验证团队需生成验证报告,证明设计满足所有规格要求,这一流程强调系统性与迭代性,随着设计复杂度的增加,验证往往占据整个项目周期的50%以上。

在验证方法中,仿真验证是最基础且广泛应用的技术,通过硬件描述语言(如Verilog、VHDL)编写测试平台,模拟设计在各种输入条件下的行为响应,仿真可分为前仿真(RTL级仿真)和后仿真(门级或布局后仿真),前者关注逻辑功能正确性,后者验证时序与物理效应影响,仿真工具如Synopsys VCS、Mentor ModelSim支持多层级仿真,支持SystemVerilog等高级语言实现复杂测试场景,仿真速度较慢,难以覆盖所有状态空间,尤其对于大规模设计。

为解决仿真覆盖率的瓶颈,形式化验证应运而生,该方法通过数学推理证明设计在特定属性下的正确性,而非通过穷举测试,典型技术包括模型检查(如Cadence JasperGold)和等价性检查(如Synopsys Formality),模型检查可自动验证有限状态机(FSM)的安全性、死锁等属性,而等价性检查则比较RTL设计与综合后网表的功能一致性,形式化验证擅长发现极端corner case,但计算资源消耗大,且需明确定义属性,适用于特定模块的深度验证。

另一种重要技术是硬件加速验证,通过FPGA原型或专用硬件平台提升验证速度,FPGA原型验证将设计映射到FPGA芯片中,运行接近实速的测试,适用于软件驱动的大规模场景验证,如SoC的系统级功能测试,硬件仿真器(如Synopsys ZeBu)则提供更灵活的调试环境,支持复杂协议与高带宽数据交互,加速验证显著缩短了验证周期,但FPGA资源有限,需进行设计分割与适配,且调试复杂度较高。

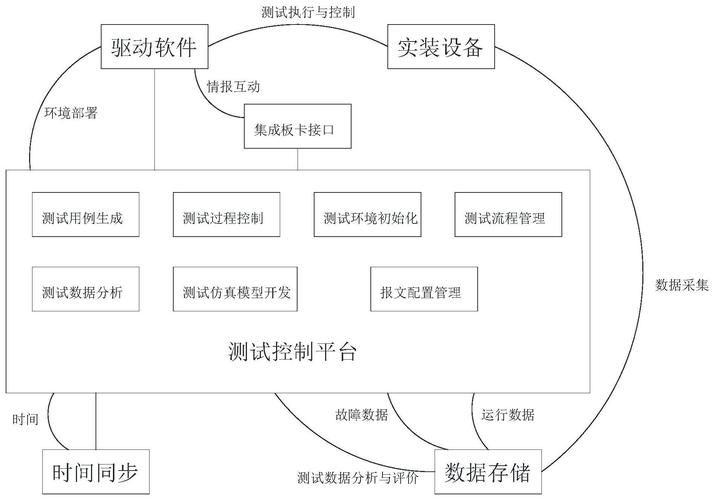

针对复杂系统级设计,基于平台的验证(Platform-Based Verification)成为主流,该方法搭建包含处理器、总线、外设的虚拟平台,通过SystemC、UVM(Universal Verification Methodology)构建可重用的验证组件,UVM作为行业标准,提供了标准化的验证框架,支持随机化测试、自检查评分板及覆盖率驱动的验证流程,虚拟平台可早期集成软件,实现硬件与软件的协同验证,同时支持虚拟原型(Virtual Prototype)技术,在硬件设计阶段提供高性能的软件开发环境。

验证覆盖率分析是评估验证完备性的关键指标,功能覆盖率(Functional Coverage)通过定义覆盖组(Covergroup)监控设计特性(如状态机跳转、总线事务类型)的执行情况;代码覆盖率(Code Coverage)则统计语句、分支、条件、触发器、状态机等元素的执行情况,覆盖率数据需与验证计划关联,未覆盖的场景需补充测试用例,现代验证工具支持覆盖率合并与分析,帮助团队聚焦高风险区域。

低功耗验证是当前SoC设计的重点,随着动态电压频率调节(DVFS)、电源门控(Power Gating)等技术的广泛应用,需验证设计在不同功耗模式下的行为一致性,低功耗验证技术包括UPF(Unified Power Format)描述功耗意图、通过LPV(Low-Power Verification)工具检查功耗管理单元(PMU)逻辑、以及验证睡眠模式唤醒序列的正确性,还需确保功耗优化不影响功能与时序。

时序验证是保证设计在目标工艺下满足频率要求的关键,静态时序分析(STA)通过计算路径延迟(组合逻辑延迟、时钟偏斜、建立/保持时间)来识别时序违规,工具如Synopsys PrimeTime支持多模式、多角落(PVT)分析,考虑工艺、电压、温度变化对时序的影响,对于高速接口,还需进行信号完整性(SI)分析,包括串扰、反射、电源噪声等,确保物理设计满足电气规范。

随着AI、5G等应用的兴起,验证技术面临新挑战,AI辅助验证通过机器学习算法分析历史缺陷数据,预测高风险区域,优化测试向量生成,形式化验证与仿真加速的融合(如形式化引导的仿真)可提升验证效率,基于云的验证平台提供了弹性计算资源,支持大规模分布式仿真,验证方法学(如UVM 1.2)持续演进,支持更高效的验证组件复用与自动化流程。

硬件验证技术是一个多元化的体系,涵盖仿真、形式化验证、硬件加速、平台验证等方法,结合覆盖率分析、低功耗验证、时序验证等专项技术,形成从功能到性能、从模块到系统的完整验证链,随着设计复杂度的提升,验证技术正向智能化、自动化、协同化方向发展,以应对日益增长的验证挑战。

相关问答FAQs

Q1:为什么硬件验证在芯片设计中占据如此重要的地位?

A1:硬件验证是确保芯片功能正确性的关键环节,随着设计规模扩大(如SoC集成数十亿晶体管)和功能复杂度提升(如多核处理器、高速接口),潜在缺陷呈指数级增长,验证不足可能导致流片失败或产品召回,造成数千万甚至上亿美元损失,硬件与软件的深度集成要求验证早期介入,确保系统级功能正确性,验证已成为芯片项目成功与否的决定性因素,通常占据项目周期50%-70%的资源投入。

Q2:形式化验证与仿真验证的主要区别是什么?如何选择?

A2:形式化验证通过数学方法证明设计在给定属性下的正确性,适用于有限状态空间、高安全性要求的场景(如控制逻辑、协议验证),能发现仿真难以覆盖的极端corner case,但计算资源消耗大且需明确定义属性,仿真验证则通过模拟输入输出来验证功能,适用于大规模设计、复杂场景测试(如软件驱动测试),但覆盖率有限且速度较慢,选择时需根据设计特性:对于状态机、仲裁器等关键模块,可采用形式化验证;对于数据通路、存储器等大规模模块,则以仿真为主,辅以形式化验证检查特定属性,两者结合可形成互补,提升验证效率与可靠性。