Altera技术支持作为全球领先的可编程逻辑解决方案提供商,Altera(现已被Intel收购,成为Intel PSG部门)为全球客户提供全方位的技术支持服务,助力工程师高效完成FPGA、SoC及相关芯片的设计与应用,其技术支持体系以客户需求为核心,覆盖设计全生命周期,从方案选型、开发工具使用到硬件调试、系统优化,提供多维度、专业化的 assistance,确保客户项目顺利推进,以下从服务内容、支持形式、资源体系及典型案例等方面详细阐述Altera技术支持的价值与实践。

技术支持的核心内容与服务形式

Altera技术支持的服务内容围绕FPGA开发的关键环节展开,形成覆盖“设计-实现-测试-部署”全流程的闭环支持体系,主要服务内容包括:

-

方案设计与选型支持:根据客户应用场景(如工业控制、通信、汽车电子、人工智能等),协助选择合适的FPGA器件系列(如Stratix、Arria、Cyclone)、SoC芯片(如Arria 10 SoC、Cyclone 10 GX)及相关配套IP核(如PCIe、DDR4、以太网),支持团队会提供器件对比表、性能参数分析及成本评估,帮助客户平衡性能、功耗与成本需求,针对高速数据处理场景,可推荐支持多通道DDR4接口的Stratix 10 GX系列,并提供带宽计算工具辅助验证。

-

开发工具链支持:Altera的核心开发工具Quartus Prime是技术支持的重点领域,支持团队提供工具安装指导、版本兼容性说明(如Quartus Prime Pro与Standard版本的区别)、HLS(高层次综合)工具(如OpenCL SDK)的使用技巧,以及针对特定功能的优化建议,对于设计中常见的综合失败、时序收敛问题,支持团队会通过日志分析、时序报告解读,提供约束文件(SDC)修改建议或时序优化方案。

-

IP核与参考设计支持:Altera提供数千个经过验证的IP核,如Nios II嵌入式处理器、DSP Builder、高速收发器IP等,技术支持团队协助客户完成IP核的配置、集成与调试,例如在Arria 10 SoC中配置HPS(硬处理器系统)与FPGA部分的接口通信,或使用PCIe IP核实现与主机的数据传输,提供丰富的参考设计(如基于FPGA的图像处理系统、电机控制方案),客户可直接基于参考设计进行二次开发,缩短开发周期。

(图片来源网络,侵删)

(图片来源网络,侵删) -

硬件设计与调试支持:针对硬件原理图设计、PCB布局布线、信号完整性(SI)和电源完整性(PI)问题,支持团队提供设计规范指导,如FPGA电源轨的退电容值计算、高速差分信号的等长约束等,在硬件调试阶段,协助使用Signal Tap II、Logic Analyzer等工具进行信号抓取与分析,定位复位异常、数据冲突等问题,某客户在DDR3接口调试中遇到数据错误,支持团队通过协助分析眼图和时序裕量,调整PCB布线长度并优化PLL参数,最终解决问题。

-

系统级优化与问题定位:对于复杂系统(如多FPGA协同、异构计算平台),技术支持团队提供跨模块的协同设计建议,协助解决多时钟域同步、数据一致性等问题,针对性能瓶颈,可提供逻辑优化(如流水线设计)、资源复用方案,或利用FPGA的硬化功能(如 hardened PCIe控制器)提升系统吞吐量。

技术支持的形式与资源体系

Altera技术支持通过多元化的服务形式,确保客户能够便捷获取所需帮助:

-

多渠道响应支持:客户可通过官方支持门户提交服务请求(SR),获得专属支持工程师的跟进;同时提供邮件支持、电话支持及在线聊天服务,针对紧急问题启动快速响应机制(如4小时内的初步反馈),对于企业级客户,还提供专属技术支持经理,协调资源解决复杂问题。

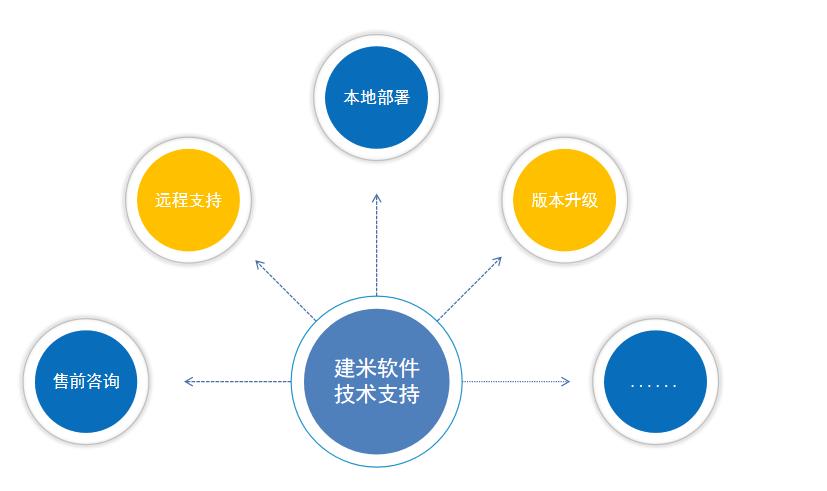

(图片来源网络,侵删)

(图片来源网络,侵删) -

在线资源与知识库:Altera官网提供丰富的技术文档,包括数据手册、应用笔记(AN)、设计指南(DG)和勘误表(ERR),应用笔记《AN-734: DDR3 SDRAM Interface Implementation》详细说明了DDR3接口的设计要点;设计指南《DP-125: High-Speed PCB Design Guidelines》则提供了PCB布局的规范,官网还提供培训视频、技术博客及社区论坛,客户可自主搜索解决方案或参与技术讨论。

-

培训与认证体系:Altera定期举办线上/线下培训课程,涵盖FPGA基础设计、高级时序优化、SoC开发等内容,并提供认证考试(如Altera FPGA Designer Certification),通过培训,工程师可系统掌握开发技能,减少基础问题的咨询量。

-

合作伙伴生态支持:与全球数千家第三方设计服务公司、IP供应商及板卡厂商合作,构建完整的生态系统,客户可通过合作伙伴获得定制化开发板、IP核授权或专业设计服务,技术支持团队则协调合作伙伴与客户的对接,确保服务一致性。

典型案例分析

某工业自动化设备厂商在开发基于Cyclone 10 GX FPGA的高速数据采集系统时,面临以下挑战:需要同时处理4路200MHz ADC数据,并通过千兆以太网实时传输至上位机,初期设计中,数据传输存在丢包问题,且FPGA资源占用率过高,客户通过Altera技术支持提交服务请求后,支持团队提供了以下解决方案:

- 数据流优化:建议采用乒乓缓冲结构,将ADC数据交替存储到双端口RAM中,减少数据传输冲突;

- 以太网IP配置:协助优化千兆以太网MAC IP的参数,启用Jumbo帧功能并调整DMA传输 burst size,提升数据吞吐量;

- 时序约束调整:通过分析时序报告,对关键路径添加约束条件,并使用Quartus Prime的时序优化功能(如物理综合),将FPGA逻辑利用率从85%降至70%,同时满足时序要求。

客户系统实现了无丢包数据传输,开发周期缩短30%。

相关问答FAQs

Q1:如何解决Quartus Prime中“Failed to fit the design”的错误?

A:该错误通常由资源不足、时序约束冲突或设计代码问题导致,可按以下步骤排查:① 检查资源使用报告,确认逻辑单元、DSP块或BRAM是否超限;② 使用TimeQuest分析器查看时序违例,调整SDC约束或优化关键路径;③ 检查代码中的组合逻辑环路或异步设计,综合时添加流水线优化;④ 若仍无法解决,可尝试降低时序要求(如设置更宽松的Slack)或升级更高容量的FPGA器件。

Q2:Altera FPGA与SoC在开发流程上有何主要区别?

A:Altera SoC(如Arria 10 SoC)集成了硬核处理器系统(HPS,基于ARM Cortex-A9)和FPGA逻辑,开发流程需兼顾HPS与FPGA的协同设计:① 需使用SoC EDS工具链配置HPS(如启动方式、外设驱动);② FPGA部分与HPS的通信需通过AXI总线接口(如HPS-to-FPGA桥接),需使用QSys工具构建系统;③ 调试时需同时使用ARM DS-5(调试HPS)和Quartus Prime Signal Tap II(调试FPGA逻辑),而纯FPGA开发无需HPS配置,流程更聚焦于逻辑设计与时序优化。