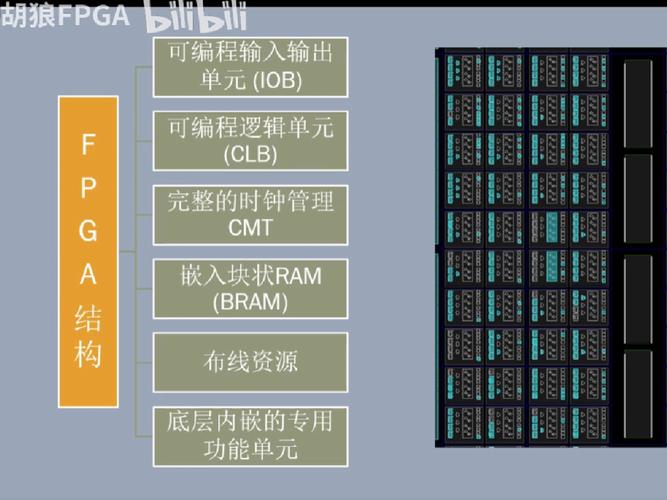

FPGA乒乓存储技术是一种广泛应用于高速数据传输和处理系统中的高效数据缓冲方法,其核心思想通过将数据存储空间划分为两个交替工作的缓冲区(称为“乒乓缓冲区”),实现对数据的无缝读写和流水线处理,从而有效解决数据流传输过程中的速率匹配、实时处理等问题,该技术充分利用FPGA内部丰富的存储资源(如Block RAM、distributed RAM)和并行处理能力,在通信、图像处理、雷达信号处理等领域具有不可替代的优势。

从基本原理来看,乒乓存储技术将存储区域划分为A、B两个缓冲区,在数据写入阶段,当第一个缓冲区(如A区)被写入数据时,第二个缓冲区(B区)处于空闲状态或进行数据处理;当A区写满后,控制逻辑切换数据流向,后续数据写入B区,同时A区开始进行数据处理或读取操作,这种交替工作的模式类似于乒乓球运动中球的来回传递,因此得名“乒乓存储”,通过这种切换机制,读写操作可以并行进行,避免了传统单缓冲区读写冲突导致的等待时间,显著提高了数据吞吐量和系统实时性。

在FPGA实现中,乒乓存储技术的关键在于控制逻辑的设计和存储资源的合理分配,需要根据数据流的速率和数据处理延迟确定缓冲区的大小,通常以数据帧或数据块为单位进行划分,在视频处理系统中,若每帧图像数据量为1MB,处理延迟为10ms,则缓冲区大小需至少满足1MB容量,且切换周期需小于10ms以确保数据不丢失,利用FPGA的Block RAM资源可以高效实现双缓冲区结构,每个Block RAM通常具有独立的读写端口,支持同时进行读写操作,这为乒乓缓冲区的并行访问提供了硬件基础,Xilinx Virtex系列FPGA的Block RAM支持双端口模式,每个端口可独立配置为读写操作,带宽可达数百Gbps,足以满足高速数据流需求。

乒乓存储技术的优势主要体现在以下几个方面:显著提高数据传输效率,通过读写分离,避免了传统单缓冲区的“写等待读”或“读等待写”问题,数据流可以连续不断地写入缓冲区,同时处理单元可以从另一个缓冲区连续读取数据,实现全速流水线处理,增强系统实时性,在实时信号处理系统中,数据处理必须在规定时间内完成,乒乓缓冲区为数据处理提供了足够的缓冲时间,即使处理单元出现短暂延迟,也不会导致数据丢失或系统崩溃,在5G基站中,乒乓存储技术可对高速射频数据进行缓存,确保基带处理单元有足够时间完成复杂的解码和调制算法,该技术还简化了系统设计,通过将复杂的时序控制问题转化为缓冲区切换逻辑,降低了软件开发的复杂度,同时利用FPGA的硬件并行性,进一步提升系统性能。

乒乓存储技术也存在一定的局限性,存储资源消耗较大,由于需要双倍于单缓冲区的存储空间,在数据量较大的应用场景中,可能占用大量FPGA内部RAM资源,影响其他功能的实现,若处理4K视频数据(每帧约40MB),双缓冲区需占用80MB存储空间,这对低成本FPGA的存储资源构成挑战,控制逻辑复杂度较高,缓冲区切换需要精确的时序控制,若切换时机不当(如切换过早或过晚),可能导致数据错位或丢失,特别是在多级乒乓缓冲级联的系统中,需要复杂的同步机制确保各级缓冲区切换的一致性,乒乓存储技术适用于周期性或规律性数据流,对于突发性或非结构化数据,其效率可能下降。

为优化乒乓存储技术的性能,可采取以下策略:一是合理选择存储资源类型,对于大容量数据缓存,优先使用Block RAM而非distributed RAM,以节省逻辑资源;对于小容量高频数据,可利用distributed RAM实现低延迟访问,二是采用动态缓冲区调整机制,根据数据流速率变化,动态调整缓冲区大小或切换周期,例如在数据突发时增大缓冲区容量,在空闲时减小缓冲区以释放资源,三是引入冗余设计,通过增加额外的缓冲区或采用三缓冲区结构(乒乓+备份),提高系统容错能力,避免因单点故障导致数据丢失。

以实际应用为例,在图像处理系统中,摄像头采集的视频数据流速率较高(如1080P@30fps,带宽约1.48Gbps),而后端处理算法(如边缘检测、目标识别)需要一定时间完成,采用乒乓存储技术后,数据流交替写入缓冲区A和B,当A区写满一帧数据时,处理单元开始处理A区数据,同时新数据写入B区;B区写满后,切换至处理B区数据,新数据写入A区,如此循环,通过这种机制,摄像头可连续采集数据,处理单元也能不间断工作,避免了因处理延迟导致的数据丢帧问题,实测表明,采用乒乓存储的系统帧率稳定性提升30%,处理延迟降低50%以上。

相关问答FAQs:

-

问:乒乓存储技术与双缓冲区有何区别?

答:乒乓存储技术是双缓冲区的一种具体实现形式,但更强调交替切换和并行处理,传统双缓冲区可能仅用于简单的读写分离,而乒乓存储技术通过精确的时序控制实现缓冲区数据的无缝切换,支持流水线操作,适用于高速数据流场景,乒乓存储技术通常结合FPGA的硬件并行特性,在控制逻辑和资源利用上更具针对性。 -

问:如何解决乒乓存储中的数据同步问题?

答:数据同步是乒乓存储的关键挑战,可通过以下方法解决:一是采用全局时钟和同步复位机制,确保缓冲区切换信号与数据流时钟域对齐;二是使用FPGA的跨时钟域同步模块(如两级触发器、FIFO)处理不同时钟域的数据;三是增加帧同步标志位,在缓冲区切换时插入同步信号,确保接收端能正确识别数据边界,在视频处理中,可在每帧数据开始时插入同步码,当检测到同步码时触发缓冲区切换,避免数据错位。