集成电路设计技术与工具

集成电路设计是将电子系统(如CPU、手机芯片、AI加速器等)的功能和性能要求,转化为具体物理电路(版图)的复杂过程,这个过程高度依赖于先进的设计技术(方法论)和强大的EDA(Electronic Design Automation,电子设计自动化)工具。

我们可以从以下几个维度来理解这个领域:

第一部分:设计理念与核心思想

在深入了解具体技术和工具之前,先理解几个贯穿整个设计流程的核心思想至关重要。

-

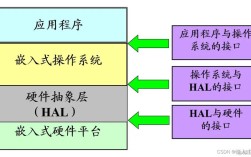

抽象分层

- 理念:将极其复杂的系统分解为多个层次,每一层都只关注其特定的功能和接口,而忽略底层细节,这是管理复杂性的唯一方法。

- 层次结构(从上到下):

- 系统级:定义芯片的功能、性能、功耗和成本目标,使用C/C++/SystemC等语言进行建模和算法验证。

- 架构级/微架构级:设计实现系统功能的具体模块和互连方式,CPU的流水线结构、Cache的大小和替换策略。

- 寄存器传输级:描述数据在寄存器之间的流动和变换,这是数字电路设计的核心层次,使用硬件描述语言如Verilog或VHDL。

- 逻辑门级:将RTL代码映射到基本的逻辑门(与、或、非、异或等)和触发器。

- 晶体管级:用晶体管(如MOS管)来设计逻辑门和基本模拟单元。

- 物理版图级:描述晶体管在硅片上的精确几何位置和连接,这是最终可以制造的图形。

-

设计方法论

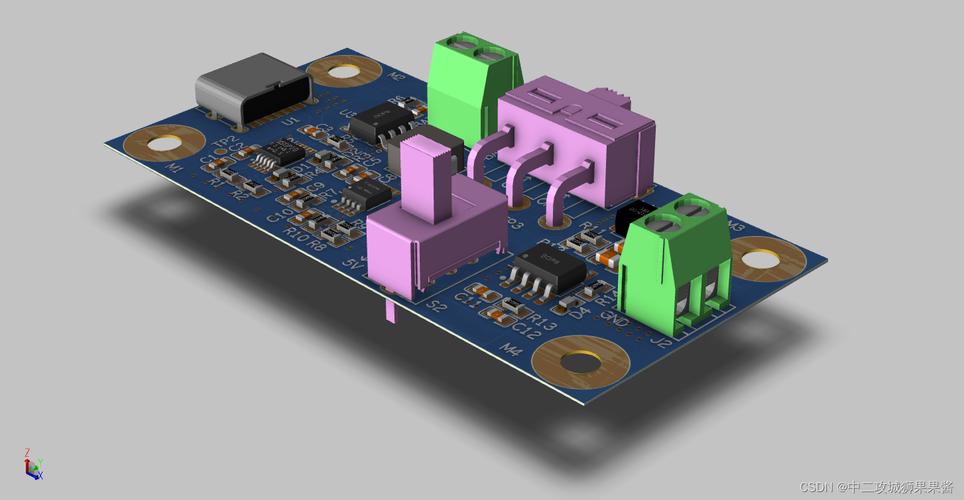

(图片来源网络,侵删)

(图片来源网络,侵删)- 自顶向下:从系统级定义开始,逐步向下细化到物理实现,这是现代IC设计的主流方法。

- 自底向上:从基本单元库(如标准逻辑门、SRAM单元)开始,组合构建更复杂的模块,最终形成系统,这种方法在单元库开发或特定模块复用时使用。

- 前端/后端分离:

- 前端:负责逻辑和功能设计,主要工作在RTL及以上层次,关注功能正确性、时序和面积。

- 后端:负责物理实现,包括布局布线、物理验证等,关注时序收敛、功耗和可制造性。

-

设计收敛

- 理念:确保设计的逻辑功能、时序性能、物理布局和功耗目标在设计的各个阶段都保持一致,最终能够成功流片并按预期工作,这是整个设计流程的终极目标。

第二部分:IC设计核心流程与技术

一个典型的IC设计流程可以分为以下关键阶段,每个阶段都有其独特的技术和挑战。

规格定义与架构设计

- 目标:明确芯片要做什么,达到什么性能指标(如主频、算力、功耗预算)。

- 关键技术:

- 性能建模与分析:使用C/C++/SystemC进行算法级建模,评估架构方案的优劣。

- 微架构设计:确定数据通路、控制逻辑、存储器层次结构等。

- 常用工具:

- 建模与仿真:MATLAB/Simulink (系统级建模),SystemC (系统级C++建模),C/C++ (算法验证)。

RTL设计与验证

这是数字设计的核心,将架构设计转化为可综合的硬件描述语言代码。

- 目标:编写出功能正确、时序清晰、易于综合的RTL代码。

- 关键技术:

- 硬件描述语言:Verilog 和 VHDL 是行业标准,SystemVerilog 是 Verilog 的超集,增加了面向对象验证等强大功能,已成为现代验证的主流。

- 功能验证:确保RTL代码的行为与设计规格完全一致,这是整个设计流程中最耗时、最关键的一步。

- 仿真:通过测试激励驱动设计,观察输出是否符合预期。

- 形式验证:通过数学方法证明两个设计(如RTL和门级)在功能上等价,或证明某段代码不存在某些bug,速度快,但覆盖率有限。

- 综合:将RTL代码自动转换成由逻辑门和触发器组成的网表。

- 常用工具:

- 仿真器:Synopsys VCS, Siemens Questa (原Mentor Modelsim/QuestaSim), Cadence Xcelium。

- 形式验证工具:Synopsys VC Formal, Cadence JasperGold。

- 综合工具:Synopsys Design Compiler, Cadence Genus。

物理设计

将逻辑网表转化为实际的物理版图,并确保所有设计目标(时序、功耗、面积)都能满足。

- 目标:在芯片面积内,合理放置所有单元,并连接所有导线,同时满足时序和功耗要求。

- 关键技术:

- 低功耗设计:使用电源门控、时钟门控、多电压域 等技术来动态关闭或降低不活跃模块的电压/频率,从而降低功耗。

- 时序分析:分析电路中信号从输入到输出的延迟,确保在最坏情况下也能满足时序要求(建立/保持时间)。

- 物理综合:在布局布线过程中进行逻辑优化,更好地实现时序收敛。

- 常用工具:

- 综合与优化:Synopsys Design Compiler, Cadence Genus (带物理综合功能)。

- 布局布线:Synopsys IC Compiler, Cadence Innovus, Siemens (原Mentor) Precision。

- 物理验证:包括DRC(设计规则检查)、LVS(版图与电路图对比),工具:Synopsys IC Validator, Cadence Voltus, Siemens Calibre。

验证与签核

在最终提交制造之前,进行最后一轮全面、严苛的检查。

- 目标:确保最终的物理版图是100%正确且可制造的。

- 关键技术:

- 静态时序分析:在不仿真的情况下,通过计算路径延迟来全面检查时序,比仿真更快速、更全面。

- 物理验证:确保版图符合代工厂的制造规则,并且版图电路图与逻辑网表一致。

- 功耗分析:精确计算芯片在典型工作模式下的总功耗。

- 常用工具:

- 静态时序分析:Synopsys PrimeTime, Cadence Tempus。

- 物理验证:如上所述,Calibre和IC Validator是行业标准。

- 功耗分析:Synopsys PrimeTime PX, Cadence Joules.

测试与可制造性设计

为芯片设计测试电路,并确保版图易于制造。

- 目标:提高芯片的良率和测试覆盖率。

- 关键技术:

- 可测试性设计:如扫描链,将时序单元串联起来,便于外部测试设备控制和观测内部状态。

- 内建自测试:在芯片内部集成测试电路,用于测试存储器或逻辑功能。

- 可制造性设计:通过在版图中添加“dummy”金属、优化天线效应等方式,帮助代工厂更稳定地生产出符合规格的芯片。

- 常用工具:

- DFT工具:Synopsys TestKompress, DFT Compiler。

- DFM工具:通常集成在布局布线工具中,如IC Compiler, Innovus。

第三部分:关键EDA工具生态链

EDA工具是IC设计的“手术刀”和“显微镜”,其市场由少数几家巨头垄断。

| 公司 | 主要工具 | 应用领域 |

|---|---|---|

| Synopsys (新思科技) | VCS (仿真器), Design Compiler (综合), IC Compiler (布局布线), PrimeTime (时序分析), Verdi (调试), DFT Compiler (可测试性设计) | 数字设计全流程的绝对领导者,尤其在高端数字领域。 |

| Siemens EDA (原Mentor Graphics) | Questa (仿真器), Calibre (物理验证/DRC&LVS), Tessent (测试), Pyxis (布局布线) | 物理验证和测试领域的王者,Calibre是业界的黄金标准。 |

| Cadence (铿腾电子) | Xcelium (仿真器), Genus (综合), Innovus (布局布线), Tempus (时序分析), **Joules |