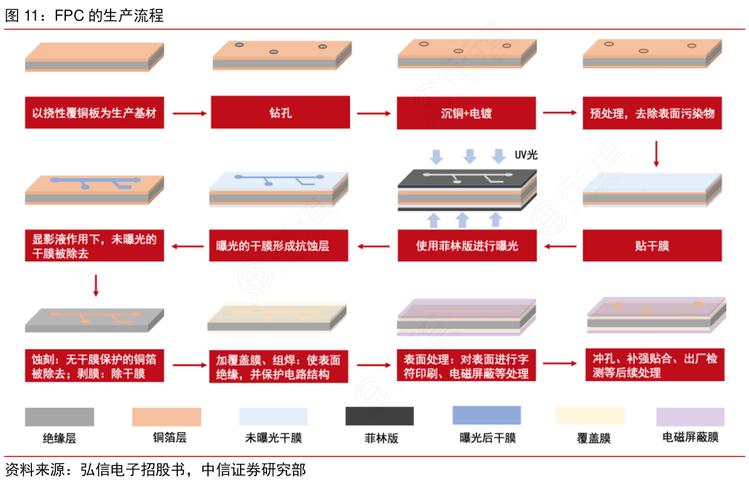

fpc技术要求及标准是柔性印制电路板设计与制造过程中的核心依据,涵盖了材料选择、结构设计、电气性能、机械可靠性及环保合规等多个维度,其目的是确保FPC在复杂应用场景中稳定工作并满足长期使用需求,以下从关键技术要求和主流标准体系两方面展开详细说明。

FPC关键技术要求

材料要求

FPC的材料直接决定其性能和适用场景,核心包括基材、覆盖膜、胶粘剂和导体材料,基材常用聚酰亚胺(PI)和聚酯(PET),其中PI耐温性(-200℃~400℃)和尺寸稳定性更优,适用于高可靠性领域;PET成本低但耐温性较差(-100℃~150℃),多用于消费电子,覆盖膜需与基材匹配,厚度通常为12.5μm~50μm,要求与基材粘接强度≥1.0N/mm,胶粘剂分环氧树脂和丙烯酸类,前者耐化学性强,后者柔韧性佳,导体材料以电解铜(ED铜)和压延铜(RA铜)为主,ED铜成本低但延展性差,RA铜适合动态弯折场景,铜箔厚度常见1oz(35μm)、0.5oz(18μm)等。

结构设计与尺寸精度

FPC结构分为单层、双层、多层及刚柔结合板,需根据弯折次数、安装空间设计叠层结构,动态弯折区域应采用RA铜和低模量胶粘剂,弯折半径需≥铜厚度的10倍(如35μm铜箔弯折半径≥0.35mm),尺寸精度方面,线宽/线距公差通常为±10%(线宽≥0.1mm时),孔径公差±0.05mm,外形轮廓公差±0.1mm,对于多层板,层间对位精度要求±0.05mm,避免短路或开路。

电气性能要求

电气性能包括导体电阻、绝缘电阻、耐电压和介电常数等,导体电阻需符合IPC-6012标准,例如1oz铜箔、10mm长度的导线,电阻应≤5.8mΩ,绝缘电阻在湿热处理后(85℃/85%RH,96h)需≥100MΩ,耐电压测试(如AC 500V/1min)无击穿或飞弧,高频应用(如5G)还需控制介电常数(Dk≤3.5)和介质损耗(Df≤0.02),确保信号完整性。

机械可靠性要求

机械可靠性是FPC长期使用的关键,需通过弯折测试、剥离强度和振动测试等,动态弯折测试中,样品经10万次弯折(弯折半径R=1mm,速度次/min)后,导体电阻变化率应≤10%,覆盖膜与基材的剥离强度≥1.2N/mm,导体与基材的剥离强度≥0.8N/mm,还需通过振动测试(10Hz~2000Hz,0.5G加速度)和冲击测试(峰值加速度50G,持续时间11ms),无断裂或虚焊。

环境与环保要求

FPC需满足RoHS、REACH等环保指令,限制铅、镉、汞等有害物质含量(铅≤1000ppm,镉≤100ppm),需通过盐雾测试(5%NaCl溶液,35℃,48h)和高温高湿测试(85℃/85%RH,1000h),确保在恶劣环境下性能稳定,焊接性方面,可焊性测试后焊料覆盖率需≥95%,无润湿不良。

主流标准体系

国际标准

- IPC标准:IPC-6012《柔性印制板分规范》详细规定了FPC的性能分级(Class 1~3,Class 3为最高可靠性等级)、测试方法和验收标准;IPC-FC-23《柔性电路材料规范》明确了基材、覆盖膜等材料的技术指标。

- IEC标准:IEC 61249系列规定基材的燃烧性(如UL94V-0等级)和热分解温度(Td≥300℃)。

- ISO标准:ISO 9001质量管理体系和ISO 14001环境管理体系是FPC制造企业的基础认证标准。

行业标准

- JEDEC标准:JESD22-A104用于FPC的跌落测试,模拟电子设备意外跌落时的机械应力。

- 汽车电子标准:AEC-Q100针对车载FPC,要求通过-40℃~125℃的温度循环测试(1000次循环)和耐振动测试(1000Hz,20G加速度)。

- 消费电子标准:苹果、华为等企业制定的内部标准,如对FPC弯折寿命(动态弯折20万次)和抗化学性(耐受汗液、酒精腐蚀)提出更高要求。

企业定制标准

部分企业根据产品特性制定特殊标准,如医疗电子FPC需通过ISO 13485医疗器械质量管理体系认证,生物相容性测试(ISO 10993)要求无细胞毒性;航空航天FPC需符合MIL-STD-810G标准,耐受极端温度(-65℃~200℃)和真空环境。

相关问答FAQs

Q1:FPC的动态弯折寿命如何通过设计和工艺提升?

A:提升动态弯折寿命需从材料和结构优化入手:①选用RA铜箔(延展性比ED铜高30%)和低模量丙烯酸胶粘剂,减少弯折时的应力集中;②动态弯折区域避免尖角设计,采用圆弧过渡(弯折半径≥铜厚10倍);③铜箔厚度控制在0.5oz(18μm)以下,基材厚度选择25μm~50μm薄型PI;④制造时采用激光切割代替机械冲孔,避免毛刺引发裂纹;⑤通过退火处理消除铜箔内应力,最终可满足20万次以上弯折需求(符合Class 3可靠性等级)。

Q2:FPC在高频信号传输中如何控制信号完整性?

A:高频FPC(如5G基站、毫米波雷达)需从设计和材料两方面控制信号完整性:①选用低介电常数(Dk≤3.5)和低介质损耗(Df≤0.02)的PI基材,如DuPont Pyralux AP;②采用差分走线设计,线宽/线距控制在8mil/8mil以内,阻抗公差±10%;③避免走线90度直角,采用45度弯折或圆弧过渡;④在信号层增加接地屏蔽层,层间间距控制在5mil~8mil,减少串扰;⑤通过阻抗仿真软件(如ADS、HFSS)优化布线,最终确保插入损耗≤0.1dB/in@10GHz,回波损耗≤-20dB@10GHz。