DC-DC转换器作为电力电子系统的核心组成部分,其关键技术直接决定了电源系统的效率、可靠性、体积及成本,以下从拓扑结构、控制技术、磁性元件设计、功率器件选型及热管理五个维度展开详细分析。

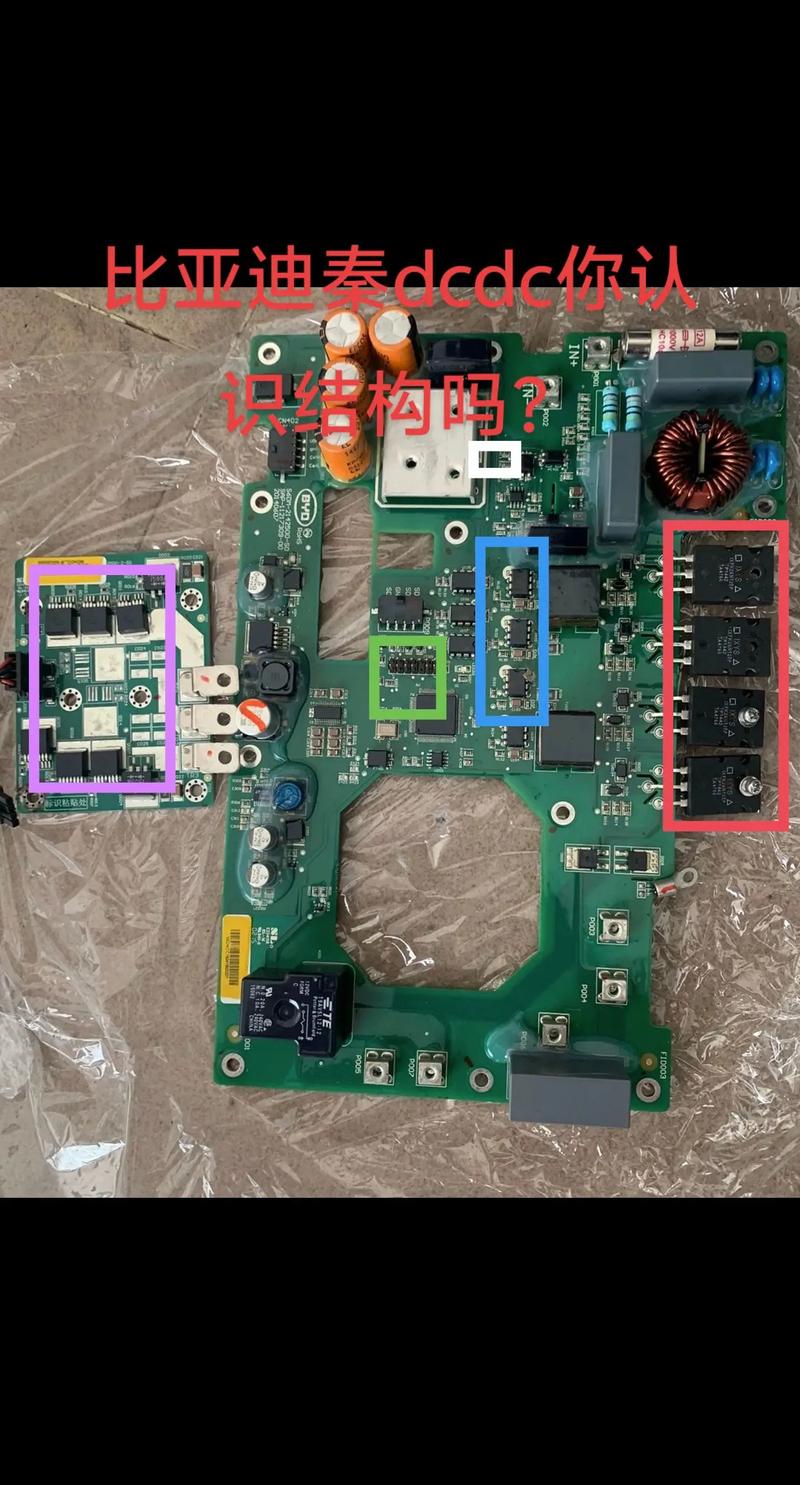

拓扑结构技术

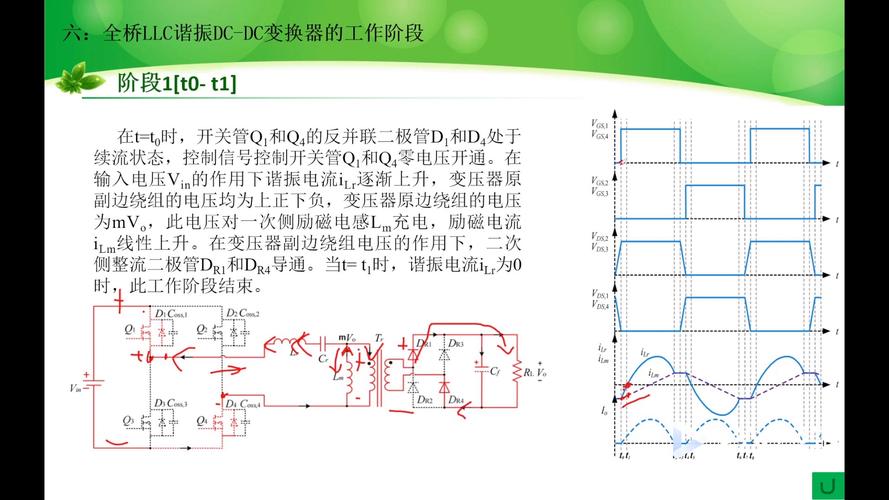

拓扑结构是DC-DC转换器的骨架,需根据输入输出电压范围、功率等级及隔离需求进行选择,非隔离型拓扑中,Buck(降压)电路结构简单,效率可达95%以上,适用于高压输入低压输出场景;Boost(升压)电路通过电储能实现电压提升,常用于光伏电池与储能系统的接口;Buck-Boost(升降压)电路则兼具两者功能,但存在输入输出电流脉动大的问题,隔离型拓扑以Flyback(反激)和Forward(正激)为代表,前者结构简单适用于小功率(<100W),后者通过变压器磁芯复位技术可传输更大功率;LLC谐振拓扑凭借软开关特性在中大功率(200W-3kW)领域效率超98%,成为新能源汽车OBC和服务器电源的主流选择,拓扑选择需权衡功率密度、动态响应及EMC性能,例如同步整流技术可显著降低导通损耗,但需增加驱动电路复杂度。

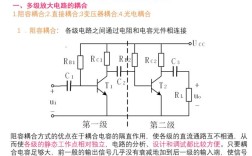

控制技术

控制策略是DC-DC转换器的“大脑”,直接影响输出精度与动态响应,电压型控制仅输出电压反馈,结构简单但负载调整率较差;电流型控制加入电感电流内环,可有效抑制输入电压波动,但需斜率补偿防止次谐波振荡,数字控制通过DSP或FPGA实现,相比模拟控制具有更高灵活性:可支持自适应PID算法、多模式切换(如轻载时进入PFM模式降低功耗)及通信接口(如I2C、PMBus),但需考虑ADC采样精度和计算延迟带来的影响,移相控制全桥拓扑通过调节桥臂相位差实现ZVS(零电压开关),大幅降低开关损耗,适合高频化设计,现代控制技术如模型预测控制(MPC)进一步提升了系统在非线性负载下的鲁棒性。

磁性元件设计

磁性元件(电感、变压器)是DC-DC转换器的储能核心,其性能制约着功率密度与效率,磁芯材料选择需兼顾高频损耗与饱和磁通密度,铁硅铝(Sendust)磁芯在100-500kHz频段损耗较低,而纳米晶磁芯适用于高功率密度场景,绕组设计需采用利兹线或扁平铜线减少趋肤效应损耗,变压器匝数比需满足输入电压范围要求,同时考虑漏感对开关管电压应力的影响,磁集成技术(如耦合电感)可减小元件数量,例如在交错并联Buck电路中,耦合电感能将输入电流纹波降低40%以上,热仿真分析必不可少,需确保磁芯工作温度低于居里点,避免电感量急剧下降。

功率器件选型

功率器件的选型需综合导通电阻(Rds(on))、开关速度及寄生参数,MOSFET是主流开关器件,SiC MOSFET相比传统Si MOSFET具有更低的导通损耗和更高的开关频率(可达1MHz以上),可使电源体积缩小50%,但成本较高;GaN HEMT则凭借高电子迁移率优势,在快充适配器中实现65W功率下体积仅19cm³,二极管选用时,SiC肖特基二极管的反向恢复电荷(Qrr)仅为硅基二极管的1/10,可大幅降低关断损耗,驱动电路设计需考虑米勒效应,采用负压驱动防止误导通,同时优化死区时间以避免桥臂直通。

热管理技术

热管理是保障DC-DC转换器长期可靠运行的关键,功率损耗主要由导通损耗(Pcond=I²R)、开关损耗(Psw=½CV²f)和磁芯损耗(Pcore=KeBf^α)构成,需通过热仿真软件(如ANSYS Icepak)精确计算,散热方式需根据功率密度选择:自然散热适用于低功率(<10W),强制风冷可满足50W-500W需求,而液冷则用于高功率密度(>10W/cm³)场景,PCB布局需遵循“热流路径最短”原则,将功率器件与散热器直接接触,采用厚铜层(≥2oz)和热过孔(Via Array)快速导热,热界面材料(TIM)的选择也至关重要,导热硅脂的热阻需低于0.5℃·cm²/W。

关键技术参数对比表

| 技术指标 | Buck电路 | LLC谐振电路 | Flyback电路 |

|---|---|---|---|

| 功率范围 | 10W-3kW | 200W-6kW | 5W-150W |

| 峰值效率 | 92%-96% | 96%-99% | 85%-92% |

| 开关频率 | 100kHz-1MHz | 100kHz-500kHz | 50kHz-200kHz |

| 功率密度 | 5-15W/cm³ | 15-30W/cm³ | 3-8W/cm³ |

| 成本 | 低 | 高 | 极低 |

相关问答FAQs

Q1:为何LLC谐振拓扑在中大功率电源中应用广泛?

A:LLC谐振拓扑通过谐振电感、电容及变压器励磁电感实现开关管的零电压开关(ZVS),大幅降低了开关损耗,同时变压器原边电流为正弦波,减小了器件电流应力,其宽范围调压能力适应不同输入电压需求,且输出整流二极管可实现零电流开关(ZCS),进一步提升了效率,这些特性使其在服务器电源、新能源汽车充电桩等对效率和功率密度要求严苛的场景中成为首选。

Q2:如何解决DC-DC转换器高频化带来的EMI问题?

A:高频化(>500kHz)会显著增加EMI干扰,需从“抑制-传导-辐射”三方面解决:1)优化PCB布局,采用接地平面(Ground Plane)和差分走线,减小环路面积;2)输入输出端添加共模电感和X/Y电容组成的滤波网络,共模电感需选择高磁导率铁氧体磁芯(如NiZn);3)开关管两端并联RC缓冲电路(Snubber)或使用有源钳位技术,抑制电压尖峰;4)金属屏蔽罩可有效减少辐射干扰,同时通过合理选择元件封装(如0402替代0603)降低寄生参数,展频技术(Spread Spectrum)通过调制开关频率,可将EMI能量分散到更宽频带,满足CISPR 32等标准要求。