基于22纳米光刻技术的半导体制造工艺代表了集成电路产业从传统平面晶体管向三维结构过渡的关键节点,这一技术节点在2010年代初期由英特尔、台积电等厂商率先实现量产,标志着摩尔定律在物理和经济双重约束下的延续性突破,22纳米工艺的核心在于通过多重曝光、FinFET(鳍式场效应晶体管)等创新技术,解决了传统平面晶体管在缩微过程中面临的漏电流、功耗控制及量子隧穿效应等难题,为移动计算、高性能处理器和物联网芯片的发展奠定了基础。

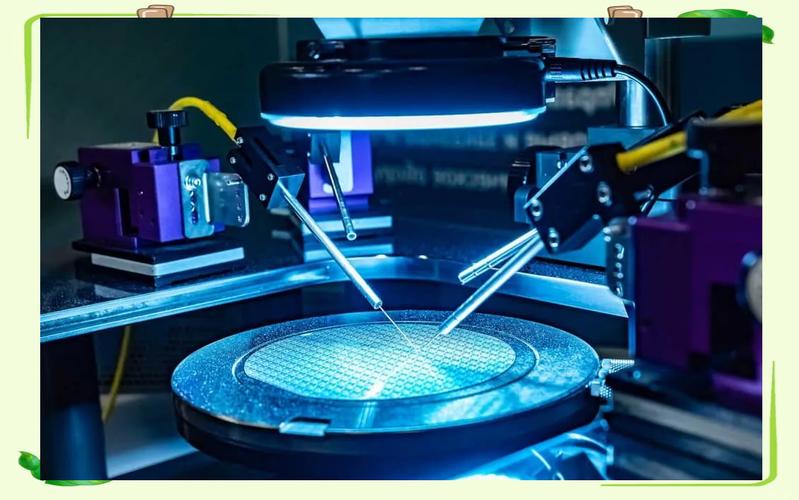

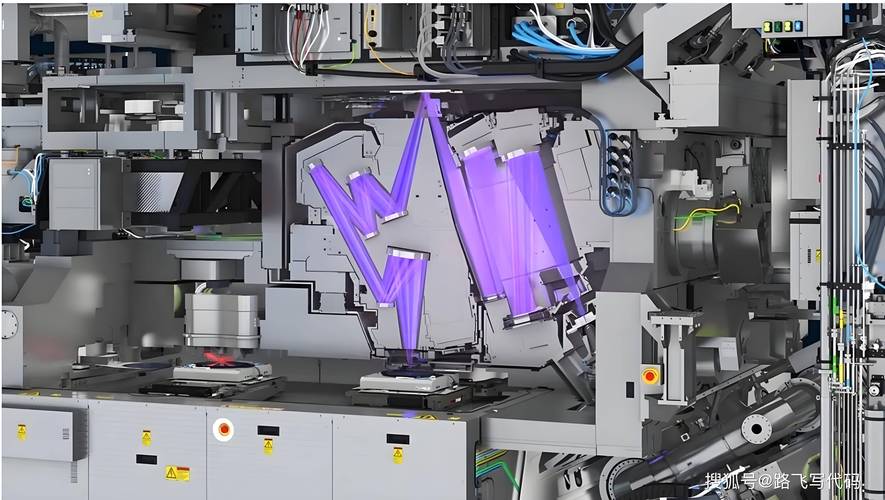

从技术实现路径来看,22纳米光刻技术以193纳米浸没式光刻(Immersion Lithography)为基础,结合多重曝光(如双曝光或四曝光)工艺,将原本难以直接印刷的精细图形分解为多次曝光步骤叠加完成,在逻辑芯片制造中,多晶硅栅极的线条宽度可通过两次曝光技术将22纳米节距图形转移至晶圆表面,同时配合相移掩模(PSM)和光学邻近效应修正(OPC)算法,弥补光刻衍射导致的图形失真,与之前的32纳米工艺相比,22纳米技术将晶体管密度提升了约2倍,同时通过引入高k金属栅(HKMG)材料替代传统的二氧化硅栅介质和 polysilicon 栅极,有效降低了栅极漏电流,提升了驱动性能和功耗比。

在晶体管结构革新方面,22纳米工艺全面采用FinFET架构,这是应对短沟道效应的核心突破,传统平面晶体管的沟道宽度仅能通过二维方向缩微,而FinFET通过在硅衬底上垂直“生长”出类似鱼鳍的纳米级沟道,通过栅极的三维包裹结构实现对沟道电流的更精准控制,这种结构使得22纳米节点的晶体管在关态漏电流降低90%的同时,开态驱动电流提升20%以上,尤其适合低功耗移动芯片的需求,以英特尔在2012年推出的22纳米 Ivy Bridge 处理器为例,其首次将三栅极(Tri-Gate)FinFET技术应用于大规模生产,晶体管数量超过14亿个,功耗较前代产品降低50%,为超极本等轻薄设备的发展提供了可能。

22纳米工艺的产业链配套也标志着半导体制造生态的成熟,光刻设备领域,ASML的 NXT:1950i 浸没式光刻机通过数值数值孔径(NA)提升至1.35,配合双重曝光技术实现了22纳米节距的图形印刷;材料方面,电子束光刻胶、先进刻蚀气体(如CF4、SF6)及化学机械抛光(CMP)浆料等关键材料的性能同步优化,满足了高精度图形转移和表面平整度的要求,22纳米节点的良率控制达到可量产水平(gt;90%),使得单晶圆制造成本控制在合理范围内,为消费级芯片的普及创造了条件。

在应用层面,22纳米技术覆盖了从高端处理器到基础芯片的广泛领域,除了英特尔酷睿系列处理器,台积电在2025年量产的22纳米工艺也应用于苹果A7芯片(用于iPhone 5s),首次在移动端实现64位计算架构;在物联网领域,22纳米低功耗芯片支持蓝牙、Wi-Fi等无线连接的长期续航,推动智能穿戴设备的市场扩张;在汽车电子中,该工艺的高可靠性满足了ADAS(高级驾驶辅助系统)对芯片性能与稳定性的双重需求,22纳米工艺的成熟为后续14纳米、10纳米等更先进节点的研发积累了技术经验,例如FinFET结构的优化、多重曝光工艺的简化等,均是在22纳米基础上迭代而来。

尽管当前3纳米、5纳米等更先进技术已实现量产,但22纳米工艺在特定领域仍具有不可替代性,其成熟的技术生态、较低的制造成本以及对模拟电路、射频电路的良好兼容性,使其成为电源管理芯片、传感器、微控制器(MCU)等“非主流”芯片的理想选择,据SEMI(国际半导体产业协会)数据,2025年全球22纳米节点芯片市场规模仍超过100亿美元,主要来自汽车电子和工业控制领域的需求增长。

相关问答FAQs

Q1:22纳米光刻技术与之前的32纳米技术相比,核心突破有哪些?

A1:22纳米技术的核心突破在于三个方面:一是晶体管结构从平面转向FinFET(三栅极架构),通过三维栅极包裹沟道解决了短沟道效应,大幅降低漏电流;二是引入高k金属栅(HKMG)材料,替代传统多晶硅栅极和二氧化硅栅介质,提升栅极控制能力并减少功耗;三是光刻工艺采用193纳米浸没式多重曝光技术,实现22纳米精细图形的印刷,同时结合OPC算法提升图形精度,这些改进使22纳米芯片在性能、功耗和集成密度上较32纳米提升显著,例如功耗降低50%,晶体管密度提升2倍。

Q2:22纳米工艺在当前先进制程竞争中是否仍有应用价值?

A2:是的,22纳米工艺在特定领域仍具有重要价值,其成熟的技术生态和较低的制造成本(约为7纳米、5纳米节点的1/3至1/2),使其成为电源管理芯片、微控制器(MCU)、传感器等对成本敏感且不需要极致算力的芯片的理想选择;22纳米工艺对模拟电路、射频电路的兼容性优于更先进的数字工艺,适合汽车电子、工业控制等高可靠性场景;部分物联网设备、穿戴式产品对功耗和成本的要求高于性能,22纳米技术能提供“够用且经济”的解决方案,因此未来5-10年仍将保持稳定的市场需求。