这是一种在现代电子系统,特别是高密度印刷电路板测试中至关重要的技术,我会从以下几个方面为您全面解析:

- 为什么需要边界扫描?—— 解决的痛点

- 边界扫描是什么?—— 核心思想

- 如何实现?—— JTAG架构

- 工作原理是怎样的?—— TAP控制器

- 边界扫描能做什么?—— 主要应用

为什么需要边界扫描?—— 解决的痛点

在边界扫描技术出现之前,测试电路板主要依赖“在线测试”(In-Circuit Testing, ICT),ICT通过在电路板上设置大量的物理探针,直接与元器件的引脚接触来进行测试,但随着技术的发展,这种方法遇到了几个难以逾越的障碍:

- 高密度封装:像BGA(球栅阵列封装)、QFN(无焊盘封装)等元器件的引脚隐藏在芯片下方,物理探针根本无法接触到。

- 高密度电路板:元器件之间的间距越来越小,探针针床的制作成本极高,甚至无法制造。

- 混合信号板:模拟、数字、高频信号线混杂在一起,使用物理探针很容易引入噪声,影响测试精度,甚至损坏电路。

- 系统级测试:当多个芯片通过高速总线(如SPI, I2C, USB)连接时,很难在板级对单个芯片的功能进行全面测试。

为了解决这些难题,联合测试行动小组提出了边界扫描测试技术,并最终形成了国际标准 IEEE 1149.1(也常被称为 JTAG 标准)。

边界扫描是什么?—— 核心思想

边界扫描的核心思想非常巧妙:不直接测试芯片内部的逻辑,而是测试芯片与外界的连接通道。

我们可以把一个具有边界扫描功能的芯片想象成一个“黑盒子”,这个芯片的每个输入/输出引脚(即芯片的“边界”)都被一个特殊的单元所“监视”和控制,这个单元就是边界扫描单元。

每个边界扫描单元本质上是一个移位寄存器位,它串联成一个巨大的“移位寄存器环”,环绕在芯片的四周,这个环被称为边界扫描寄存器。

这个寄存器环有四个关键端口:

- 数据输入:从上一个芯片的TDI(Test Data In)或上一个扫描单元传来。

- 数据输出:传给下一个芯片的TDO(Test Data Out)或下一个扫描单元。

- 连接到芯片内部逻辑:与芯片内部的实际输入/输出引脚相连。

- 连接到芯片外部引脚:与PCB上的物理引脚相连。

通过这个“扫描环”,我们就可以在不影响芯片内部正常工作的情况下,将数据移入或移出芯片,从而精确地控制和观测每个引脚的状态。

如何实现?—— JTAG架构

符合IEEE 1149.1标准的芯片内部都包含一个称为测试访问端口 的特殊硬件模块,TAP是控制和访问边界扫描逻辑的统一入口,一个标准的TAP包含以下四个(或更多)必需的信号线:

- TCK (Test Clock):测试时钟,为整个边界扫描逻辑提供同步时钟。

- TMS (Test Mode Select):测试模式选择,这是一个控制信号,在TCK的上升沿有效,用于决定TAP控制器在不同测试状态之间如何转换(是进入数据移位状态,还是回到运行-复位状态)。

- TDI (Test Data In):测试数据输入,用于向边界扫描寄存器或指令寄存器串行移入数据。

- TDO (Test Data Out):测试数据输出,用于从边界扫描寄存器或指令寄存器串行移出数据。

- *TRST (Test Reset)**:可选的异步复位信号,用于将TAP控制器复位到初始状态。

除了这四个信号,芯片内部还包含两个核心寄存器:

- 指令寄存器:用于接收和存放当前要执行的指令。

EXTEST(外部测试)、SAMPLE/PRELOAD(采样/预加载)、BYPASS(旁路)等。 - 数据寄存器:这是一个“多路复用”的寄存器,它包含了多个子寄存器,其中最重要的就是边界扫描寄存器,通过指令寄存器选择,我们可以将数据通路切换到不同的数据寄存器上。

工作原理是怎样的?—— TAP控制器

TAP控制器是JTAG架构的“大脑”,它是一个状态机,由TMS信号驱动,在TCK的上升沿进行状态转换,它负责协调指令的加载和数据的移位。

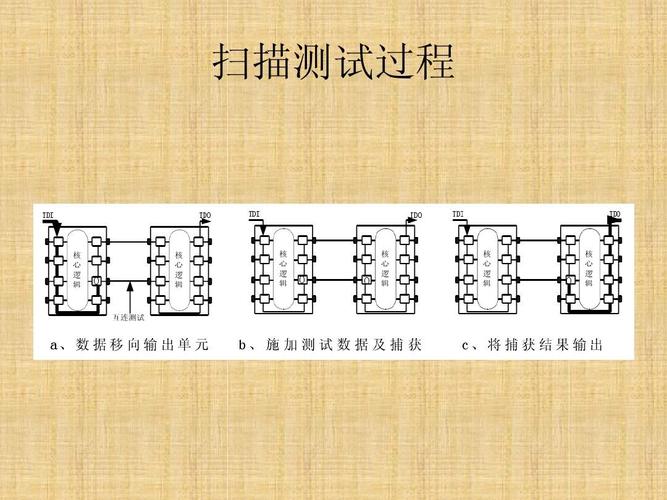

一个典型的测试流程如下:

- 进入测试模式:通过特定的TMS序列,将TAP控制器从“测试-逻辑-复位”状态启动。

- 加载指令:

- 将TMS设置为“移位指令”状态。

- 通过TDI串行移入要执行的指令码(

EXTEST指令的编码)。 - 指令被加载到指令寄存器中。

- 执行指令并移入数据:

- TAP控制器根据指令,将数据通路切换到相应的数据寄存器(

EXTEST指令会选择边界扫描寄存器)。 - 再次进入“移位”状态,通过TDI将测试数据串行移入整个扫描链,数据会依次通过所有芯片的边界扫描单元,就像流水线一样。

- TAP控制器根据指令,将数据通路切换到相应的数据寄存器(

- 捕获数据:

当测试数据被加载到引脚上后,TAP控制器会进入“捕获”状态,将引脚上实际响应的电平(高/低/高阻)捕获回边界扫描单元中。

- 移出数据:

- TAP控制器再次进入“移位”状态,将捕获到的响应数据从边界扫描寄存器中,通过TDO串行移出。

- 对比分析:将移出的响应数据与预期的“黄金”数据进行比较,从而判断芯片之间的连接(如短路、开路、引脚功能错误)是否正常。

- 退出测试模式:通过TMS序列,将TAP控制器复位,芯片恢复到正常运行状态。

边界扫描能做什么?—— 主要应用

JTAG技术已经从最初的“测试”功能,演变为现代电子系统开发和维护中不可或缺的“瑞士军刀”。

-

互连测试

- 功能:这是JTAG最基本的功能,测试PCB上不同芯片引脚之间的连接是否正确。

- 可检测故障:引脚之间的短路、开路、粘连、错位等物理连接问题。

- 执行指令:

EXTEST。

-

内建自测试

- 功能:许多复杂的芯片(如FPGA、RAM、PLL)内部集成了自测试逻辑,JTAG可以启动这些芯片的内部自测试程序,验证其自身功能是否正常。

- 执行指令:

INTEST(测试芯片内部逻辑)、厂商自定义的BIST指令。

-

器件编程

- 功能:这是JTAG最广泛的应用之一,通过JTAG接口,可以在线对Flash、EEPROM等存储器进行编程,以及对FPGA、CPLD等可编程逻辑器件进行配置。

- 优点:无需将芯片从板上取下,方便快捷,是量产编程和固件更新的主要手段。

-

系统调试

- 功能:现代处理器(如ARM Cortex-M/A系列)和FPGA都集成了嵌入式调试模块,这些模块通过JTAG TAP访问。

- 可实现:

- 设置断点:在代码的特定行暂停程序执行。

- 单步调试:逐行执行代码。

- 查看/修改寄存器和内存:实时检查系统状态。

- 实时追踪:记录程序的执行流和变量变化(需要额外硬件支持)。

-

系统观测

- 功能:在不干扰芯片正常运行的情况下,捕获并观测其引脚上的实时信号。

- 执行指令:

SAMPLE/PRELOAD,可以“快照”下某个时刻所有引脚的状态,用于分析信号质量和时序问题。

边界扫描测试技术是一项革命性的发明,它通过在芯片的I/O边界增加一个可测试的“扫描环”,巧妙地解决了高密度电路板测试的难题。

- 核心:IEEE 1149.1标准,定义了TAP和边界扫描架构。

- 基础:TAP控制器(状态机)和围绕芯片的边界扫描寄存器链。

- 能力:从最初的互连测试,扩展到BIST、器件编程、系统调试和系统观测,成为贯穿电子产品设计、生产、维护全生命周期的关键技术。

可以说,没有JTAG,现代复杂电子系统的开发、测试和调试将变得异常困难甚至不可能,它是数字系统工程师必须掌握的核心技能之一。