SoC的低功耗设计是一个贯穿芯片整个生命周期的系统性工程,涉及到架构、设计、验证、制造、软件等多个层面,其核心思想是:在满足性能和功能的前提下,尽可能减少能量消耗。

我们可以从以下几个关键层面来理解这些技术:

架构与系统级设计

这是最高层次的功耗管理,决定了SoC的整体功耗“天花板”。

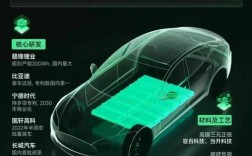

a. 异构计算

这是现代高性能SoC(如手机SoC)最核心的架构设计之一。

- 原理:在SoC中集成多种不同类型的处理器核心,每种核心针对特定任务进行优化。

- CPU(中央处理器):如高性能的Cortex-A系列核心,处理复杂计算和操作系统任务。

- GPU(图形处理器):处理图形渲染和并行计算。

- DSP(数字信号处理器):高效处理音频、视频等信号处理任务。

- NPU(神经网络处理器):专门用于AI推理计算。

- RISC-V / Cortex-M 等低功耗核心:用于处理简单的后台任务、传感器数据采集等。

- 低功耗优势:对于简单的后台任务(如计步器、接收消息),无需唤醒笨重的高性能CPU,而是使用低功耗核心来处理,从而极大地节省了功耗,只有在需要高性能时(如玩游戏、跑AI大模型),才唤醒对应的专用核心。

b. 近阈值计算

- 原理:传统的CMOS电路工作在“过阈值区”,电压和电流都较高,近阈值计算将电压和频率降低到晶体管的“阈值电压”附近。

- 低功耗优势:功耗与电压的平方成正比(P ∝ CV²f),大幅降低电压可以带来功耗的指数级下降,虽然性能也会随之下降,但对于一些对性能不那么敏感但对功耗极其敏感的应用(如IoT传感器),这是极佳的权衡。

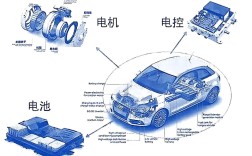

c. 电源门控

- 原理:当SoC中的某个模块(如GPU、DSP)长时间不工作时,直接切断其供电电源,这比仅仅让模块进入低功耗状态更彻底。

- 低功耗优势:消除了该模块的静态功耗(漏电流功耗),效果显著,但实现复杂,需要设计专门的“电源开关”电路,并且唤醒时有延迟。

d. 时钟门控

- 原理:在不工作的模块上关闭其时钟信号,由于没有时钟翻转,模块内部的动态功耗(主要由开关活动产生)被完全消除。

- 低功耗优势:实现相对简单,是应用最广泛的低功耗技术之一,通常与动态电压频率调整结合使用。

设计与实现级技术

这些技术是在RTL(寄存器传输级)和物理设计阶段实现的。

a. 动态电压频率调整

- 原理:根据当前任务的负载,动态调整工作电压和频率,看视频时提高频率,待机时降低频率甚至关闭核心。

- 低功耗优势:这是动态功耗管理的核心,在性能需求低时,通过降低频率来降低动态功耗(P ∝ CV²f),同时配合降低电压,实现功耗的“阶梯式”下降。

b. 多电压域

- 原理:将SoC划分为不同的“电压域”,每个域可以独立供电,高性能核心工作在高电压域,而外设(如UART, I2C)工作在低电压域。

- 低功耗优势:让不同性能、不同功耗需求的模块工作在最合适的电压下,避免了“一刀切”的高电压设计,从整体上降低了SoC的平均功耗。

c. 多阈值电压

- 原理:在制造工艺中,提供几种不同阈值电压的晶体管。

- 低阈值电压晶体管:开关速度快,性能高,但漏电流大(静态功耗高)。

- 高阈值电压晶体管:开关速度慢,性能低,但漏电流小(静态功耗低)。

- 低功耗优势:在关键路径上使用低Vt晶体管以保证性能,在非关键路径或静态时使用高Vt晶体管以降低漏电,这是一种在性能和静态功耗之间的精妙权衡。

d. 时钟网络优化

- 原理:时钟信号是SoC中功耗最大的信号网络之一,通过优化时钟树的布局、使用低功耗时钟门控单元、减少不必要的时钟翻转来降低时钟网络的功耗。

- 低功耗优势:直接降低系统中最主要的动态功耗来源之一。

物理与制造级技术

这些技术依赖于半导体制造工艺的进步。

a. 高κ金属栅极

- 原理:传统的栅极介质是二氧化硅(SiO2),随着工艺节点缩小,其漏电问题严重,高κ材料(如HfO₂)具有更高的介电常数,可以在物理厚度更厚的情况下实现相同的电容,从而有效抑制漏电流。

- 低功耗优势:显著降低了晶体管的静态漏电功耗,是先进工艺(如28nm及以下)能够实现低漏电的关键。

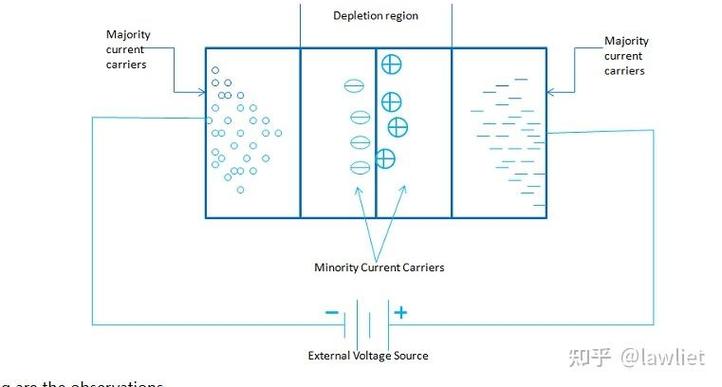

b. FinFET (鳍式场效应晶体管)

- 原理:传统的平面晶体管在工艺缩小时,栅极对沟道的控制能力变弱,导致漏电剧增,FinFET将沟道做成“鱼鳍”状的立体结构,栅极可以包裹住三个侧面的沟道,极大地增强了控制能力。

- 低功耗优势:在同等性能下,FinFET可以工作在更低的电压,从而大幅降低动态功耗,优异的栅极控制也有效抑制了漏电。

c. 硅通孔

- 原理:在传统的2D平面布局基础上,在芯片的垂直方向上制造互连通道。

- 低功耗优势:TSV极大地缩短了芯片内部长距离互连的线长,根据互连功耗公式(P ∝ C V² f * SW),电容C的减小可以直接降低功耗。

软件与系统级技术

硬件的低功耗潜力需要软件来充分释放。

a. 操作系统电源管理

- 原理:操作系统(如Linux, Android, FreeRTOS)是所有任务的调度中心,也是功耗管理的“大脑”。

- CPU频率调节:通过

cpufreq等框架,根据系统负载动态调整CPU频率和电压。 - 设备驱动管理:在不使用外设(如Wi-Fi, 蓝牙, GPS)时,通过驱动程序将其置于低功耗模式或关闭。

- 任务调度:将任务集中调度到少数几个核心上,让其他核心完全关闭或进入深度睡眠。

- CPU频率调节:通过

b. 中断与事件驱动

- 原理:改变软件的运行模式,避免让CPU通过“轮询”的方式不断检查某个事件是否发生(例如检查网络数据包),这种方式会让CPU持续处于活动状态。

- 低功耗优势:采用“中断”或“事件驱动”模式,CPU大部分时间可以处于低功耗的睡眠状态,只有当事件真正发生时(如收到网络数据包),才被中断唤醒处理,这对于IoT设备至关重要。

c. 算法优化

- 原理:软件算法本身也影响功耗,一个计算效率高的算法,可以在更短的时间内完成任务,然后让硬件尽快进入低功耗状态。

- 低功耗优势:使用更高效的图像压缩算法、AI推理模型剪枝/量化等,都能减少计算量,从而降低运行时的动态功耗。

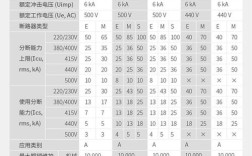

| 层面 | 核心技术 | 目标功耗 | 关键点 |

|---|---|---|---|

| 架构/系统级 | 异构计算、近阈值计算、电源门控 | 静态功耗、平均功耗 | 从根本上决定SoC的功耗特性,是顶层设计 |

| 设计/实现级 | DVFS、多电压域、多阈值电压、时钟门控 | 动态功耗、静态功耗 | 在具体实现中精细控制每个模块的功耗 |

| 物理/制造级 | 高κ/金属栅、FinFET、TSV | 静态功耗、动态功耗 | 工艺进步带来的物理极限突破 |

| 软件/系统级 | OS电源管理、中断驱动、算法优化 | 平均功耗、运行时功耗 | 释放硬件低功耗潜力,是最终用户体验的关键 |

SoC的低功耗设计是一个“自顶向下,软硬件协同”的系统性工程,没有单一的“银弹”技术,而是需要在架构、设计、工艺和软件等多个层面采用多种技术,并进行精心的权衡和优化,才能打造出既高性能又超低功耗的芯片。