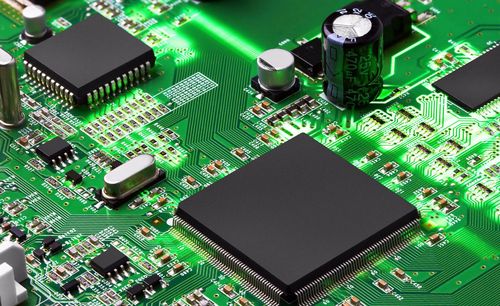

FPGA技术的发展是一个不断融合、演进的过程,其核心思想是“硬件可编程”,即在制造完成后,用户可以根据自己的需求配置其内部逻辑,实现定制化的硬件功能,这使其在灵活性上介于专用集成电路和通用处理器之间。

发展历程:从“胶水逻辑”到“计算核心”

FPGA的发展可以大致分为以下几个关键阶段:

诞生与早期探索 (1980年代)

- 技术起源:FPGA的概念源于可编程逻辑器件,如PAL、GAL等,其核心技术是查找表和SRAM配置工艺。

- 里程碑事件:

- 1985年:Xilinx公司发布了世界上第一款商用FPGA——XC2064,标志着FPGA时代的正式开启,它基于SRAM工艺,包含64个逻辑模块和2个I/O块。

- 同期竞争者:Altera(现Intel PSG)也推出了基于EEPROM工艺的MAX系列,提供了非易失性的特性。

- 特点:逻辑规模小,速度慢,成本高,主要用作简单的“胶水逻辑”,替代中小规模的数字电路。

规模扩张与性能提升 (1990年代)

- 技术驱动:半导体工艺的进步(从2μm发展到0.35μm甚至更小)使得集成度大幅提升。

- 架构创新:

- 逻辑块优化:从简单的LUT发展到更复杂的自适应逻辑模块,如Altera的LAB(Logic Array Block)和Xilinx的CLB(Configurable Logic Block),增加了触发器、多路选择器等,提高了逻辑效率和灵活性。

- 硬核IP的引入:在可编程逻辑中嵌入专用的、高性能的模块,如乘法器、RAM块、锁相环等,这使得FPGA能够胜任更复杂的数字信号处理和通信任务。

- 应用拓展:从简单的逻辑控制扩展到通信、图像处理、数据采集等领域。

SoC与3D IC的融合 (2000年代)

- 技术驱动:摩尔定律持续有效,系统级集成成为趋势。

- 里程碑事件:

- 2004年:Xilinx推出Virtex-II Pro FPGA,首次集成了PowerPC处理器硬核,开启了FPGA与处理器融合的SoC(System on Chip)时代。

- 2010年:Altera推出SoC FPGA,在FPGA中集成了ARM Cortex-A系列处理器硬核,进一步推动了FPGA在嵌入式领域的应用。

- 3D IC技术:通过硅通孔将不同工艺的芯片(如逻辑芯片、存储芯片、I/O芯片)堆叠在一起,实现更高性能、更低功耗的集成,Xilinx的UltraScale系列是早期采用3D IC技术的代表。

- 特点:FPGA不再只是一个“逻辑器件”,而是一个集成了处理器、内存、高速接口的异构计算平台。

AI与数据中心时代的爆发 (2010年代至今)

- 技术驱动:人工智能,特别是深度学习的兴起,对并行计算能力提出了前所未有的需求。

- 里程碑事件:

- 2025年:Xilinx推出UltraScale+架构,其可编程逻辑与高速接口(如PCIe 4.0)的结合,使其成为AI推理加速的理想选择。

- 2025年:赛灵思发布Alveo加速卡系列,这是专为数据中心设计的FPGA加速卡,标志着FPGA正式进入大规模数据中心市场。

- 2025年:AMD(收购了Xilinx)推出Versal ACAP(自适应计算加速平台),这是FPGA架构的一次革命性飞跃,我们将在下一部分详细阐述。

- 特点:FPGA成为AI/ML、数据中心、5G通信、高性能计算等领域的关键加速器,强调高带宽、低延迟和能效比。

当前技术趋势与架构演进

当前FPGA技术正朝着以下几个核心方向快速发展:

架构的革命:从FPGA到ACAP

- 代表产品:AMD/Xilinx的 Versal ACAP (Adaptive Compute Acceleration Platform)

- 核心思想:不再局限于“可编程逻辑 + 硬核IP”的简单叠加,而是构建一个多层次、异构、可动态重构的计算平台。

- 关键组件:

- AI引擎:由大量可编程的VLIW (Very Long Instruction Word) 核心和SIMD单元组成,专为AI和DSP负载设计,性能远超传统DSP和硬核。

- 自适应引擎:这是ACAP的灵魂,即传统的FPGA逻辑,但性能和效率大幅提升,可以动态重构以适应不同任务。

- 片上网络:取代传统的总线结构,为AI引擎、自适应引擎、I/O等提供高速、高带宽的片上通信,解决了“内存墙”和“带宽瓶颈”问题。

- 高性能I/O和接口:集成PCIe 5.0/6.0、CXL、以太网等高速接口,无缝连接CPU和系统内存。

制程工艺的极限挑战与异构集成

- 先进制程:主流厂商已采用7nm、5nm甚至更先进的工艺节点,这带来了更高的晶体管密度和更低的功耗,但也带来了巨大的挑战:

- 设计复杂性:先进工艺的设计和验证成本极高。

- 良率问题:小尺寸晶体管对工艺波动更敏感,影响良率。

- 静态功耗:漏电流问题严重。

- Chiplet(小芯片)与异构集成:为了应对先进制程的挑战,Chiplet技术成为新趋势。

- 定义:将一个大型芯片的功能拆分成多个独立的、功能更专一的“小芯片”,然后通过先进封装技术(如2.5D/3D封装)集成在一个基板上。

- 优势:

- 降低成本:可以用成熟制程生产非关键部分,降低整体成本。

- 提高良率:小芯片面积小,良率更高。

- 灵活性:可以像搭积木一样组合不同工艺、不同功能的Chiplet。

- 代表:AMD/Xilinx的Versal系列就采用了Chiplet技术,将不同的计算单元和I/O单元分别制造再集成。

EDA工具链的智能化

- 挑战:FPGA的规模和复杂性呈指数级增长,传统的人工设计和综合方法已不堪重负。

- 趋势:AI赋能的EDA工具。

- AI驱动的布局布线:利用机器学习算法,在巨大的搜索空间中寻找更优的布局布线方案,以实现更高的频率、更低的功耗和更短的时序收敛时间。

- 高层次综合:让工程师使用C++/SystemC等高级语言进行算法描述,HLS工具能自动将其转换为RTL代码,极大提升了算法和系统级设计的效率。

- 云原生设计:将FPGA设计流程迁移到云端,提供弹性计算资源、预置的IP库和协作环境,加速设计迭代。

生态系统的开放与标准化

- 挑战:FPGA开发工具链(尤其是综合、实现工具)长期被Xilinx、Intel等少数几家巨头垄断,形成了“厂商锁定”效应。

- 趋势:开源硬件生态的崛起。

- RISC-V:作为一种开源指令集架构,正在被广泛集成到FPGA中,为处理器IP提供了自由、开放的替代方案。

- 开源FPGA工具链:如SymbiFlow等项目,致力于打造一个完全开源的从HLS到比特流生成的工具链,打破商业壁垒。

- 标准化接口:CXL (Compute Express Link)等开放标准的出现,使得FPGA加速卡能够与不同厂商的CPU和内存系统更好地协同工作。

未来展望

- AI与计算融合的深化:FPGA将成为后摩尔时代AI计算的核心引擎之一,未来的FPGA将拥有更强大的AI引擎、更高效的片上网络,并支持更稀疏化、量化的模型,实现极致的能效比。

- “万物可编程” (Everything Programmable):随着ACAP架构的成熟,FPGA的应用将从数据中心扩展到更广泛的领域,如自动驾驶、工业物联网、边缘计算、量子计算控制等,任何需要硬件级定制化和高能效的场景,都可能看到FPGA的身影。

- 软件定义硬件:未来的系统将更加灵活,FPGA作为“硬件加速器”的角色将更加突出,开发者可以通过软件定义的方式,动态地调用和配置FPGA资源,以适应不断变化的算法和工作负载。

- 安全性与可信计算:随着FPGA在关键基础设施和敏感数据处理中的应用,其硬件级的安全特性(如物理不可克隆功能、可信执行环境)将变得至关重要。

FPGA技术的发展史,是一部“从补充到核心”的演进史,它从最初填补ASIC和标准逻辑器件之间空白的“胶水逻辑”,一步步成长为现代计算系统中不可或缺的异构计算加速核心。

未来的FPGA将不再是简单的“可编程门阵列”,而是集成了AI引擎、高性能I/O和智能片上网络的“自适应计算平台”,其发展将继续受到AI浪潮、摩尔定律的物理极限和开放生态三大因素的深刻影响,在灵活性、性能和能效之间不断寻求新的平衡,成为驱动未来计算创新的关键力量。