CMOS芯片驱动技术是现代电子系统的核心组成部分,它直接影响着芯片的性能、功耗、可靠性和集成度,随着半导体工艺的不断进步和应用需求的日益多样化,CMOS驱动技术也在不断演进,从简单的逻辑电平转换到复杂的高速信号传输,从低功耗设计到智能化自适应控制,其内涵和外延都在持续扩展,本文将详细探讨CMOS芯片驱动技术的关键要素、主流架构、设计挑战以及未来发展趋势。

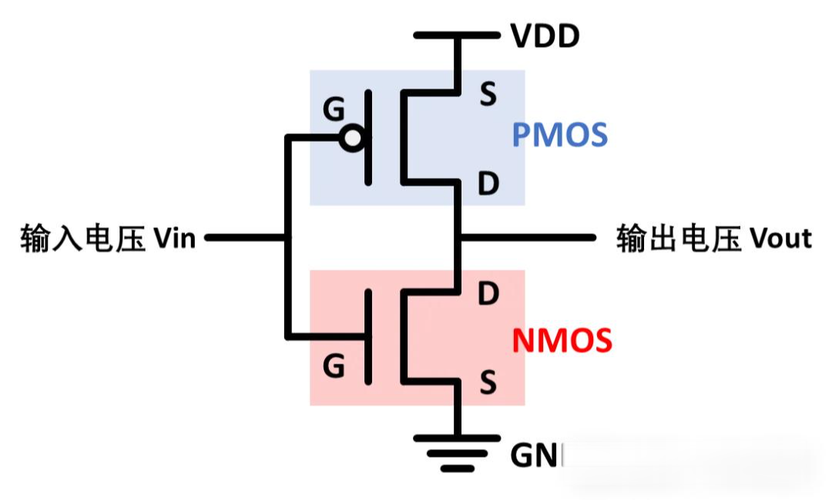

CMOS(Complementary Metal-Oxide-Semiconductor)驱动技术的基础在于CMOS工艺的对称性,即同时采用N沟道MOSFET(NMOS)和P沟道MOSFET(PMOS),利用其互补特性实现逻辑功能,一个基本的CMOS反相器就是最简单的驱动单元,它由一个PMOS管和一个NMOS管串联组成,当输入为低电平时,PMOS导通、NMOS截止,输出高电平;当输入为高电平时,PMOS截止、NMOS导通,输出低电平,这种结构具有静态功耗极低、噪声容限大、逻辑摆幅接近电源电压等优点,是构建复杂驱动电路的基础,在实际应用中,驱动负载的能力往往成为关键指标,尤其是当需要驱动大电容负载、长传输线或高功率器件时,简单的反相器结构已无法满足需求,因此需要设计更复杂的驱动电路。

驱动能力是CMOS驱动技术的核心指标之一,它取决于输出级晶体管的尺寸、驱动电压以及负载特性,晶体管的尺寸(如沟道宽度W和沟道长度L)直接影响其导通电阻Ron,W/L越大,Ron越小,驱动电流能力越强,但同时也增加了芯片面积和输入/输出电容,可能影响速度和功耗,驱动电压则决定了输出信号的摆幅和驱动电流的上限,在低压工艺下,如何保证足够的驱动能力是一个重要课题,负载特性通常表现为容性、感性和阻性,其中容性负载最为常见,如连接器的寄生电容、传输线的分布电容等,驱动容性负载时,充电和放电电流I=C(dV/dt)决定了信号上升时间和下降时间,因此需要根据负载电容大小和要求的速度,合理设计输出级晶体管的尺寸,以实现速度与功耗的平衡。

为了满足不同应用场景的需求,CMOS驱动技术发展出了多种主流架构,推挽式输出结构是最常见的一种,它由一个PMOS上拉管和一个NMOS下拉管组成,能够主动拉高和拉低输出电平,驱动能力强,响应速度快,但在某些情况下,如需要实现线与(Wire-AND)功能或防止总线冲突时,采用开漏(Open-Drain)或开源(Open-Source)结构更为合适,这种结构只有下拉管或上拉管,输出端需要通过外部上拉电阻或下拉电阻获得确定电平,常用于I2C、SMBus等总线协议,对于需要更高驱动电流的场景,如驱动LED、继电器或功率MOSFET,通常采用图腾柱(Totem-Pole)结构或集成驱动管的解决方案,图腾柱结构在推挽式基础上增加了额外的驱动管,进一步增强了电流输出能力,在一些对功耗敏感的应用中,如可穿戴设备,还会采用低功耗驱动技术,如门控时钟、动态电压频率调节(DVFS)以及自适应驱动强度调节等,根据负载和运行状态动态调整驱动电路的工作参数,以降低不必要的功耗。

随着集成电路工作频率的不断提升,信号完整性问题成为CMOS驱动技术面临的重要挑战,当驱动信号通过传输线时,如果阻抗不匹配,会发生信号反射,导致过冲、下冲、振铃等现象,严重影响信号质量,高速驱动电路通常需要集成阻抗匹配功能,如采用串联端接(Series Termination)或并联端接(Parallel Termination)技术,使输出阻抗或负载阻抗与传输线 characteristic impedance(特性阻抗)相匹配,以消除反射,信号串扰(Crosstalk)、电磁干扰(EMI)以及电源/地噪声(Power/Ground Noise)也是高速设计中需要重点考虑的问题,串扰主要由相邻信号线之间的电容耦合和电感耦合引起,通过优化布局布线、增加信号线间距、使用屏蔽线等方法可以抑制,EMI则与信号的上升/下降时间密切相关,过快的边沿会辐射更多高频噪声,因此需要在速度和EMI之间进行权衡,电源/地噪声通常由开关电流引起,通过使用去耦电容、优化电源分配网络(PDN)设计可以有效降低噪声影响。

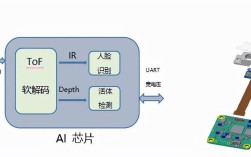

在先进工艺节点(如7nm及以下)和SoC(System-on-Chip)设计中,CMOS驱动技术面临着更为复杂的挑战,工艺尺寸的缩小导致晶体管的阈值电压(Vth)和驱动电压(Vdd)降低,噪声容限减小,对驱动电路的抗干扰能力提出了更高要求,SoC中往往包含多种不同电压域的模块,如CPU核心、内存接口、外设接口等,需要高效的电平转换(Level Shifting)技术来实现不同电压域之间的信号传输,同时避免不必要的功耗和信号完整性问题,随着3D IC、Chiplet(芯粒)等先进封装技术的兴起,芯片间互连的驱动技术也成为研究热点,需要考虑高密度互连、低功耗信号传输以及热管理等问题,为了应对这些挑战,研究人员正在探索新型驱动电路架构,如基于FinFET或GAA(Gate-All-Around)晶体管的驱动设计、采用机器学习算法进行自适应驱动控制、以及利用片上网络(NoC)技术优化片外通信的驱动策略等。

| 驱动技术类型 | 特点 | 典型应用场景 |

|---|---|---|

| 推挽式输出结构 | 主动拉高拉低,驱动能力强,速度快 | 通用数字逻辑输出,高速接口 |

| 开漏/开源结构 | 需外部上拉/下拉电阻,支持线与功能 | I2C、SMBus总线,多主机系统 |

| 图腾柱结构 | 增强驱动电流,适合大电流负载 | LED驱动,功率MOSFET栅极驱动 |

| 低功耗自适应驱动 | 动态调整驱动强度,降低静态和动态功耗 | 可穿戴设备,移动终端 |

CMOS芯片驱动技术是一个涉及电路设计、半导体工艺、信号完整性分析等多个学科的综合性技术,它在保障电子系统性能、降低功耗、提高可靠性方面发挥着至关重要的作用,随着人工智能、5G通信、物联网等新兴技术的快速发展,对CMOS驱动技术的要求将越来越高,驱动技术将继续向着高速化、低功耗化、智能化和集成化的方向演进,为构建下一代高性能电子系统提供坚实的基础。

相关问答FAQs:

问题1:为什么高速CMOS驱动电路需要进行阻抗匹配?如果不匹配会怎样? 解答:高速CMOS驱动电路进行阻抗匹配的主要目的是消除信号在传输线上的反射,当驱动器的输出阻抗(Zout)、传输线的特性阻抗(Z0)和负载阻抗(Zload)三者不匹配时,信号到达负载端时会发生反射,反射系数ρ=(Zload-Z0)/(Zload+Z0),反射回来的信号与原始信号叠加,会导致信号波形出现过冲(Overshoot)、下冲(Undershoot)、振铃(Ringing)等失真现象,严重时可能造成逻辑误判,甚至损坏电路器件,通过阻抗匹配(如Zout=Z0或Zload=Z0),可以使反射系数为零或接近零,从而确保信号能量高效、无失真地传输到负载端,保证信号完整性。

问题2:在低压CMOS工艺下(如1.2V Vdd),如何提高驱动电路的驱动能力而不显著增加功耗? 解答:在低压CMOS工艺下提高驱动能力而不显著增加功耗,可以采用以下几种策略:1)采用级联或并联晶体管结构:通过多个较小尺寸的晶体管并联来等效一个大尺寸晶体管,可以在保持总驱动能力的同时,减小输入电容,降低驱动前级电路的负担;级联结构则可以增强对晶体管的栅压驱动,提高其导通能力,2)使用电荷泵技术:通过电荷泵将局部电源电压抬高于Vdd,为驱动管提供更高的栅极驱动电压,从而在低压环境下获得更强的驱动电流,但需要注意电荷泵本身带来的功耗和面积开销,3)优化驱动电路架构:如采用自适应驱动强度控制,根据负载大小和信号跳变需求动态调整输出级晶体管的导通数量,在轻负载时减小驱动尺寸以降低功耗,在重负载时增大驱动尺寸以满足速度要求,4)利用工艺增强技术:如采用高k金属栅(HKMG)或应变硅等工艺技术,在相同尺寸下提高晶体管的载流子迁移率,从而增强驱动能力。