接地技术是电子电气系统设计中确保设备安全、抑制电磁干扰、保障信号完整性的基础性工程实践,其中信号接地作为其核心组成部分,直接关系到系统性能的稳定与可靠,信号接地的主要目的是为系统中的信号电流提供低阻抗返回路径,抑制共模干扰,降低噪声耦合,确保信号在传输过程中不失真、不衰减,从理论到实践,信号接地的设计需综合考虑频率特性、接地拓扑、接地材料等多重因素,以适应不同应用场景的需求。

信号接地的核心原理在于“等电位”与“低阻抗”,理想情况下,所有接地点应处于同一电位,避免因地电位差形成噪声电流,实际电路中存在寄生电感、电容和电阻,导致接地阻抗随频率变化,高频时,接地线的寄生电感(通常为1-10nH/mm)会感抗(XL=2πfL)显著增加,反而成为噪声耦合的路径,信号接地需根据信号频率特性选择接地策略:低频电路(<1MHz)可采用单点接地,避免形成接地环路;高频电路(>10MHz)需采用多点接地,减小接地阻抗;而混合频率电路则需采用混合接地或接地平面设计,在PCB设计中,大面积覆铜接地平面可提供极低的阻抗(lt;0.1Ω)和稳定的参考电位,同时通过过孔连接多层接地平面,进一步降低高频阻抗。

信号接地的拓扑结构直接影响系统的抗干扰能力,常见的接地拓扑包括单点接地、多点接地和混合接地,单点接地是将所有电路单元的接地线连接到同一个物理点,适用于低频模拟电路,可有效避免接地环路,但其缺点是接地线较长,高频时阻抗增大,易受电磁干扰,多点接地则是将每个电路单元就近连接到接地平面或机壳,高频时阻抗低,但可能引入接地环路,需通过隔离变压器或光电耦合器解决,混合接地结合了两者的优点,例如在低频段采用单点接地,高频段通过电容或电感实现多点接地,兼顾低频稳定性与高频抑制能力,在实际应用中,数字电路与模拟电路的接地需严格分离,避免数字噪声通过公共阻抗耦合到模拟部分,通常采用“分区接地”策略,将数字地与模拟地分别布线,最后在电源入口处或ADC/DAC芯片下方单点连接,通过磁珠或0Ω电阻实现高频隔离。

接地材料与工艺的选择对信号接地性能至关重要,接地导体需具备低电阻率(如铜的电阻率为1.68μΩ·cm)和良好的高频特性,在高频场合,趋肤效应使电流集中在导体表面,需采用镀银或镀锡铜材以降低表面阻抗,接地平面的设计需避免“长条状”走线,应采用网格或实心铜层,减少寄生电感,对于多层PCB,建议将一层或多层完整作为接地平面,信号线尽量布在相邻层,通过寄生电容耦合噪声至地,接地连接点的可靠性不容忽视,焊接点需避免虚焊,螺栓连接需确保接触压力,必要时采用导电胶或电磁密封垫降低接触电阻,在机箱接地中,需通过低阻抗接地线(截面积≥4mm²)连接至大地,接地电阻应满足安全标准(如一般设备≤4Ω,医疗设备≤0.5Ω)。

信号接地与噪声抑制的关系密不可分,共模噪声是信号系统的主要干扰源,其通过接地阻抗转化为差模噪声,叠加在信号上,通过“接地隔离”技术(如隔离变压器、光耦)可切断噪声路径,而“屏蔽接地”则需遵循“一点接地”原则,避免屏蔽层形成环路,同轴电缆屏蔽层应在中控端单点接地,防止两端电位差导致电流流动,在差分信号传输中,对称的接地设计可确保两条信号线的对地阻抗相等,抑制共模干扰,接地系统的“接地环路”问题需重点关注,当设备间通过多条接地线连接时,可能因地电位差(如雷击、电力负载变化)形成环路电流,可通过共模扼流圈、隔离变压器或取消冗余接地线解决。

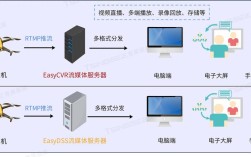

不同应用场景对信号接地的要求差异显著,在通信系统中,高频信号(如5G射频电路)需采用同轴接地或腔体接地,确保阻抗匹配(通常50Ω)和低回波损耗,医疗设备(如ECG、EEG)对信号精度要求极高,需采用浮地设计或隔离接地,防止漏电流对患者造成伤害,工业自动化环境中,强电设备(如变频器)的接地需与弱电信号系统分开,采用独立接地网,并通过浪涌保护器(SPD)抑制瞬态过电压,在汽车电子中,CAN总线等信号接地需考虑振动、温度变化对接触电阻的影响,采用星型接地或多点冗余接地,航空航天领域则要求接地系统具备轻量化、高可靠性,采用碳纤维复合材料接地或镀金接插件,确保极端环境下的性能稳定。

信号接地的测试与验证是确保设计有效性的关键环节,接地电阻测试采用四线法(开尔文法)消除接触电阻影响,测量值需符合标准,接地阻抗测试需通过网络分析仪在1MHz-1GHz频段测量,确保高频阻抗满足设计要求,噪声测试则通过示波器或频谱分析仪测量信号地与机壳地之间的噪声电压,典型值应<10mV,接地环路测试可采用电流钳测量环路电流,或通过注入噪声信号观察系统响应,对于复杂系统,可采用电磁兼容(EMC)测试,如辐射发射测试(RE)、传导抗扰度测试(CS),验证接地系统的抑制能力,测试中发现的问题需通过优化接地拓扑、增加接地过孔、更换接地材料等方式整改,直至满足指标要求。

信号接地技术的发展趋势与高频化、集成化、智能化需求紧密相关,随着5G、物联网(IoT)、人工智能(AI)等技术的普及,信号频率持续提升(毫米波频段可达100GHz以上),传统接地技术面临挑战,新型接地材料如石墨烯、超导材料的应用可进一步降低阻抗;三维(3D)接地平面通过垂直互连减少寄生电感,适用于高密度封装,智能化接地系统通过传感器实时监测接地阻抗、噪声水平,结合算法动态调整接地策略,提升系统自适应能力。“虚拟接地”技术利用运算放大器或开关电容电路模拟低阻抗参考点,在无物理接地的场景(如植入式医疗设备)中实现信号稳定传输。

相关问答FAQs:

Q1:为什么高频电路必须采用多点接地,而低频电路适合单点接地?

A:高频电路中,信号波长较短(如1GHz信号波长为30cm),接地线的寄生电感(约1nH/mm)会导致感抗(XL=2πfL)显著增加,若采用单点接地,长接地线会形成高阻抗路径,噪声难以抑制,多点接地将电路就近连接到接地平面,减小接地环路面积和高频阻抗,确保噪声快速泄放,低频电路(<1MHz)信号波长较长,接地环路影响较小,单点接地可避免多个接地点间的电位差形成环路电流,防止低频噪声耦合(如50Hz工频干扰),频率特性是选择接地拓扑的核心依据。

Q2:如何处理PCB设计中数字地与模拟地的分割问题?

A:数字地与模拟地分割需遵循“分区隔离、单点连接”原则,首先在布局时将数字电路(如MCU、FPGA)与模拟电路(如运放、传感器)分别布置在不同区域,避免数字信号线跨越模拟区,地线分割时,采用物理隔离(如沟槽)将数字地(DGND)与模拟地(AGND)分开,布线时各自独立回流,关键是在ADC/DAC芯片下方或电源入口处通过0Ω电阻、磁珠或窄桥连接两地,确保低频电位相等的同时,高频噪声被磁珠抑制(磁珠阻抗在100MHz时可达100Ω),需注意避免分割区域形成“狭长地带”,增加寄生电感,且连接点应靠近敏感器件(如运放输入端),减少数字噪声对模拟信号的干扰。