华为NPU(神经网络处理单元)技术作为人工智能计算的核心引擎,近年来经历了从专用硬件到智能计算平台的跨越式发展,其技术更新不仅推动了终端设备的智能化升级,更在云端、边缘端构建了全场景AI算力生态,从最初的寒武纪1.0到如今的达芬奇架构升级,华为NPU的迭代始终围绕“算力效率、能效比、算法适配”三大核心维度展开,通过架构创新、制程突破与生态协同,持续重塑AI计算的技术边界。

架构演进:从并行计算到异构融合的跨越

华为NPU的技术更新首先体现在计算架构的颠覆性创新,早期NPU(如麒麟970集成寒武纪MLU100)采用传统的SIMD(单指令多数据流)架构,专注于神经网络矩阵运算的并行加速,但受限于数据搬运效率和指令灵活性,难以应对复杂多变的AI模型,2025年推出的达芬奇架构(Da Vinci Architecture)则实现了质的飞跃,其核心是“3D Cube计算引擎+统一存储架构”:通过立方体计算引擎(Cube Unit)实现高密度矩阵乘法运算(支持INT4/INT8/FP16混合精度),同时通过统一内存缓冲区减少数据搬移延迟,使算力利用率提升至90%以上。

2025年发布的NPU 4.0架构进一步引入“张量加速引擎+AI CPU协同”的异构融合设计:在Cube Unit基础上新增动态稀疏计算单元,可自动识别模型中的零值元素并跳过计算,稀疏场景下算力效率提升3倍;同时通过AI CPU实时调度算力资源,将NPU与CPU、GPU的协同延迟降低40%,这种架构创新使得华为NPU在处理大语言模型(如千亿参数模型)时,能效比(每瓦算力)较前代提升5倍,为端侧AI的复杂推理提供了硬件基础。

制程与集成:从7nm到5nm+的能效革命

制程工艺的进步是华为NPU技术更新的另一核心驱动力,从麒麟990的7nm NPU(2.6 TOPS算力)到麒麟9000S的7nm+ NPU(5.2 TOPS算力),再到Mate 60 Pro搭载的NPU 5.0(基于7nm+工艺优化,算力达15.8 TOPS),制程优化与芯片集成度的提升直接推动了算力密度的跨越。

更重要的是,华为通过“芯粒技术”(Chiplet)实现了NPU的模块化集成,在昇腾910B云端AI芯片中,采用7nm Chiplet将多个NPU核心通过高速互联总线(HCCS)集成,单芯片算力达到256 TFLOPS(FP16),较前代提升4倍,同时功耗控制在300W以内,能效比提升2倍,这种“先进制程+Chiplet”的路线,既规避了先进制程的工艺风险,又实现了算力的弹性扩展,为云端大模型训练提供了高效算力支撑。

算法与生态:从单一加速到全场景适配

华为NPU的技术更新不仅局限于硬件层面,更通过算法优化与生态构建实现了“硬件-软件-应用”的全栈协同,在软件层面,华为自研的CANN(Compute Architecture for Neural Networks)计算平台实现了NPU与CPU、GPU的统一算子调度,支持TensorFlow、PyTorch等主流AI框架,并将模型编译效率提升3倍。

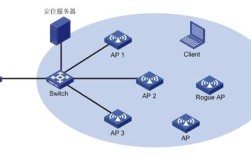

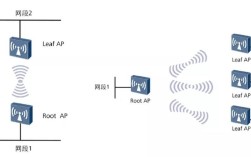

针对端侧AI的碎片化需求,华为推出了“端-边-云”协同的NPU技术体系:端侧NPU(如麒麟9010)支持INT4量化,在保持95%模型精度的前提下,功耗降低60%;边缘端NPU(如昇腾310)通过轻量化架构,可实时处理4K视频流的AI推理(如目标检测、语义分割);云端NPU(如昇腾910B)则通过千亿参数模型优化,支持GPT类大模型的分布式训练,华为还开放了NPU开发工具链(MindSpore Lite),让开发者能针对NPU特性优化模型,目前已有超过100万款应用适配华为NPU,覆盖影像、语音、自动驾驶等场景。

应用场景:从单一功能到智能体验的重塑

技术更新最终体现在用户体验的升级上,在智能手机领域,华为NPU通过“AI摄影”重构影像系统:Mate 60 Pro的NPU 5.0支持实时语义分割,可精准识别画面中的天空、人物、建筑等元素并进行独立优化,夜景拍摄速度提升3倍;在语音交互方面,NPU的端侧唤醒词识别准确率达99%,响应延迟降至100ms以内,实现“即说即响应”。

在智能汽车领域,华为NPU通过MDC(智能驾驶计算平台)实现L4级自动驾驶算力:MDC 610搭载NPU 4.0架构,算力达200 TOPS,支持16路摄像头数据实时处理,能效比较传统方案提升4倍,在云端,华为NPU已支撑起盘古大模型的训练,该模型在气象预测、药物研发等领域实现精度突破,例如台风路径预测准确率较传统方法提升15%。

技术更新对比表

| 技术维度 | 早期NPU(如麒麟970) | 当前NPU(如NPU 5.0) | 提升幅度 |

|---|---|---|---|

| 架构 | SIMD并行计算 | 3D Cube+动态稀疏+异构融合 | 算力利用率提升90% |

| 制程工艺 | 7nm | 7nm+ Chiplet集成 | 算力密度提升5倍 |

| 算力(手机端) | 8 TOPS(INT8) | 8 TOPS(INT8) | 8倍 |

| 能效比(端侧) | 5 TOPS/W | 15 TOPS/W | 6倍 |

| 软件生态 | 单框架支持 | 多框架协同+百万级应用适配 | 模型编译效率提升3倍 |

相关问答FAQs

Q1:华为NPU与GPU在AI计算中有什么区别?

A:华为NPU与GPU的设计目标和应用场景存在本质差异,NPU为神经网络计算专用硬件,采用“数据并行+架构定制”设计,擅长低精度(INT4/INT8)矩阵运算,能效比远高于GPU(例如端侧NPU能效比可达GPU的10倍以上),适合端侧实时推理;而GPU为通用图形处理器,采用“流式多处理器”架构,高精度(FP32/FP64)计算能力强,适合云端大模型训练,NPU通过CANN平台实现与CPU/GPU的异构协同,形成“端-边-云”全场景算力互补,而非替代关系。

Q2:华为NPU的动态稀疏技术如何提升算力效率?

A:动态稀疏技术是华为NPU的核心创新之一,通过“稀疏检测-稀疏计算-数据重排”三步流程实现算力倍增,具体而言,NPU在计算前会实时扫描模型权重中的零值元素,跳过无效计算并压缩数据存储;计算过程中,稀疏计算单元针对稀疏矩阵优化计算路径,减少冗余运算;计算完成后,通过硬件级数据重排确保后续计算的连续性,以BERT模型为例,稀疏化处理后算力提升3倍,同时保持模型精度无损,大幅降低了AI推理的能耗与延迟。