CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)是一种基于乘积项结构的高密度可编程逻辑器件,介于简单PLD(如PAL、GAL)与FPGA之间,具有集成度高、功耗低、开发周期短、非易失性等特点,其核心由可编程与阵列、或阵列、输出逻辑宏单元(OLMC)等组成,通过硬件描述语言(如VHDL、Verilog)或原理图设计,实现数字逻辑的灵活配置,CPLD的编程单元通常采用E²PROM或Flash技术,断电后配置信息不丢失,无需外部存储芯片即可独立运行,这使其在嵌入式系统、工业控制、通信设备等领域得到广泛应用。

从技术架构来看,CPLD内部包含多个逻辑块(LAB),每个逻辑块相当于一个独立的PAL或GAL,通过全局互连矩阵连接,实现复杂的逻辑功能,其与FPGA的主要区别在于:CPLD采用基于乘积项的固定架构,适合实现组合逻辑和状态机,而FPGA基于查找表(LUT)和分布式RAM,更适合并行数据处理和高速运算,CPLD的配置加载方式多样,支持JTAG、PS(被动串行)等接口,便于在线编程和调试,降低了开发难度。

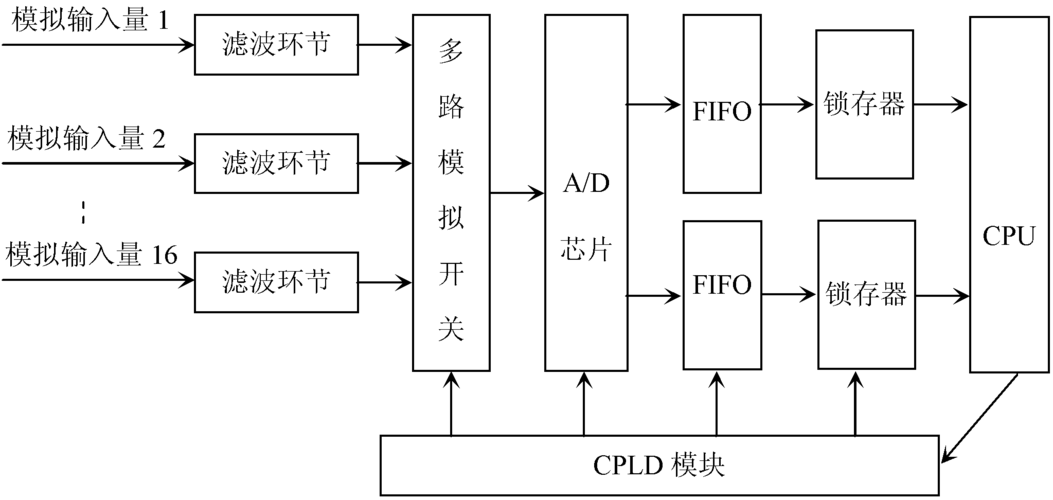

在应用层面,CPLD凭借其高可靠性和实时性,成为多个领域的核心器件,在工业自动化中,CPLD常用于实现电机控制逻辑、传感器数据采集和系统监控,例如PLC(可编程逻辑控制器)的扩展模块通过CPLD处理高速信号,响应时间可达纳秒级,满足工业现场对实时性的严格要求,通信领域方面,CPLD负责协议转换、数据帧同步和时钟管理,如在路由器中实现以太网MAC层逻辑,或光传输设备中的SDH/SONET帧处理,其非易失性特性确保了系统断电后配置不丢失,提升了设备稳定性。

消费电子是CPLD的另一大应用场景,在智能手机中,CPLD管理电源切换、按键扫描和接口扩展,例如USB Type-C接口的配置逻辑或显示器的时序控制;在可穿戴设备中,CPLD负责低功耗状态切换,延长电池续航,汽车电子领域,CPLD用于车身控制单元(BCU),实现车灯控制、门窗锁止和防盗系统的逻辑处理,其宽工作温度范围(-40℃至125℃)和抗干扰能力满足车规级要求,CPLD在航空航天、医疗设备等高可靠性场景中也有重要应用,如卫星通信系统的信号切换或医疗监护设备的数据预处理,确保系统在极端环境下的稳定运行。

为更直观展示CPLD的应用场景与优势,以下表格列举了典型应用领域及其功能需求:

| 应用领域 | 功能需求 | CPLD实现优势 |

|---|---|---|

| 工业自动化 | 高速信号处理、实时逻辑控制、多任务并行 | 纳秒级响应速度,非易失性配置,抗电磁干扰 |

| 通信设备 | 协议转换、数据帧同步、时钟恢复 | 多通道I/O支持,灵活的时序控制,低功耗设计 |

| 消费电子 | 接口扩展、低功耗管理、小型化集成 | 小封装尺寸(如QFP、BGA),快速启动,动态重构能力 |

| 汽车电子 | 宽温工作、高可靠性、安全逻辑 | 车规级认证,硬件加密功能,故障检测与保护机制 |

| 医疗设备 | 精确时序控制、抗干扰、实时数据处理 | 低延迟信号处理,符合医疗标准(如IEC 60601),可定制安全逻辑 |

CPLD的技术优势还体现在开发效率与成本控制上,相比传统ASIC(专用集成电路),CPLD无需高昂的流片费用,开发周期可缩短至数周,且支持多次擦写(通常可达1万次以上),便于设计迭代,其设计工具(如Altera Quartus、Xilinx ISE)提供丰富的IP核和仿真功能,降低了硬件设计门槛,CPLD的可编程性允许系统升级时通过软件更新逻辑,无需更换硬件,延长了设备生命周期。

CPLD也存在一定局限性,其逻辑资源(通常为数百至数千门)远小于FPGA(可达数百万门),不适合实现大规模并行算法;乘积项结构在处理复杂数据运算时效率较低,且内部RAM容量有限,难以满足高缓存需求,在需要大规模逻辑或高速数据处理的应用中,常采用CPLD+FPGA的混合架构,CPLD负责系统控制接口和配置管理,FPGA处理核心算法,实现优势互补。

随着技术的发展,CPLD正向着更高集成度、更低功耗和更强功能演进,新型CPLD集成模拟前端、高速ADC/DAC和嵌入式处理器核,形成SoC(片上系统)解决方案;3D封装技术提升了器件密度,而低功耗设计(如多电压域管理)使其更适合物联网(IoT)节点等场景,CPLD将在边缘计算、智能传感器和工业4.0等领域继续发挥关键作用,推动数字系统的智能化和小型化。

相关问答FAQs

Q1:CPLD与FPGA的主要区别是什么?如何根据需求选择?

A1:CPLD基于乘积项结构,逻辑资源少(lt;1万门),适合实现组合逻辑、状态机和简单控制,具有非易失性、低功耗和快速启动特点;FPGA基于查找表和RAM,逻辑资源丰富(可达数百万门),支持大规模并行运算和高速数据处理,但需外部配置芯片且功耗较高,选择时,若需低成本、低功耗、高可靠性的逻辑控制(如接口扩展、协议转换),优先选CPLD;若需复杂算法、并行处理(如图像处理、AI加速),则选FPGA或混合架构。

Q2:CPLD在开发过程中需要注意哪些问题?

A2:需重点关注以下几点:1)逻辑资源分配,避免因乘积项不足导致设计无法实现;2)时序约束,确保关键路径满足系统时钟要求,可通过时序分析工具优化;3)信号完整性,高速信号布线需注意阻抗匹配和串扰抑制;4)功耗管理,低功耗应用需合理配置I/O状态和时钟频率;5)调试方法,利用JTAG接口在线实时调试,结合逻辑分析仪分析信号时序。