封装技术是半导体制造中至关重要的环节,它将裸露的芯片与外部环境隔离,提供电气连接、机械保护和散热功能,从而确保芯片的稳定运行和长期可靠性,在众多封装技术中,COP封装技术因其独特的优势在现代半导体产业中占据重要地位,COP是Chip On Pad的缩写,中文译为“芯片凸块封装技术”或“芯片焊盘直接贴装技术”,其核心思想是通过在芯片焊盘上制作微小凸块(Bump),将芯片直接倒装(Flip Chip)封装基板或引线框架上,从而实现芯片与封装 substrate 之间的直接电气互连和机械固定,这种技术相较于传统的引线键合(Wire Bonding)技术,在电气性能、散热效率、尺寸 miniaturization 和可靠性方面均有显著提升。

COP封装技术的起源可以追溯到20世纪60年代,随着芯片集成度的提高和频率的提升,传统引线键合的寄生参数(如寄生电感和寄生电容)成为限制芯片性能的瓶颈,倒装芯片技术最早由IBM公司提出,并在大型计算机和高性能计算领域得到应用,早期的倒装芯片技术存在凸块制作精度低、共晶焊接可靠性差等问题,限制了其普及,直到20世纪90年代,随着凸块制作工艺(如电镀、焊膏印刷)的成熟和底部填充材料(Underfill)的发展,COP封装技术才逐渐走向商业化,并广泛应用于CPU、GPU、射频芯片、存储芯片等高性能器件中。

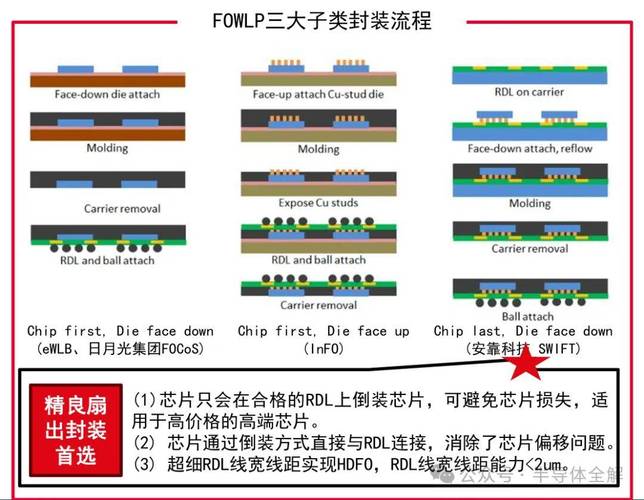

COP封装技术的核心工艺流程包括以下几个关键步骤:首先是芯片凸块制作,在芯片的铝焊盘上通过蒸发、电镀或焊膏印刷等方式制作金属凸块(通常为焊料凸块,如锡铅共晶或无铅焊料,或铜柱凸块+焊料帽),凸块的高度和直径通常在几十到几百微米之间;其次是芯片凸块再分布层(RDL)制作,对于需要I/O重分布的芯片,会在凸块上制作多层金属布线,将芯片焊盘重新分布到更合适的间距和位置;然后是倒装贴片,将制作好凸块的芯片翻转,通过精准的对位设备将凸块与封装基板上的焊盘或凸块对准,然后在回流焊炉中加热,使凸块与基板焊盘发生共晶反应或熔化焊接,形成牢固的机械和电气连接;接着是底部填充,在芯片与基板之间的缝隙中填充环氧树脂等底部填充材料,通过固化后提供机械支撑,缓解因芯片与基板热膨胀系数(CTE)不匹配引起的应力,提高封装可靠性;最后是模塑(Molding)、打标(Marking)、切割(Dicing)等后道封装工序,完成最终的封装结构。

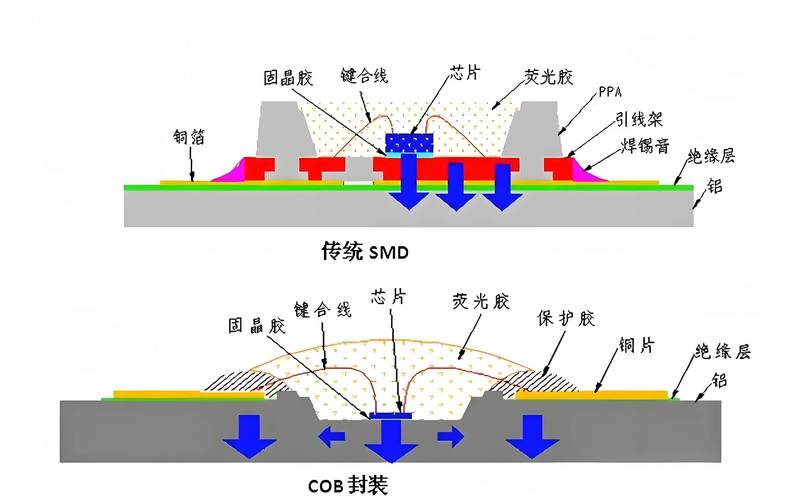

与传统引线键合封装相比,COP封装技术具有多方面的显著优势,在电气性能方面,由于芯片与基板之间的互连长度极短(仅为凸块高度,通常为50-200μm),大大降低了寄生电感和寄生电容,从而提高了信号传输速度,降低了信号延迟和功耗,特别适合高频、高速芯片(如5G射频芯片、高速存储器)的应用,在散热性能方面,COP封装通过凸块实现了芯片有源区与基板之间的直接热传导,热量可以快速从芯片传递到基板和散热器,而传统引线键合的热量需要通过引线和塑封材料传导,散热路径较长,热阻较大,根据测试数据,相同功率下,COP封装的芯片结温(Junction Temperature)可比引线键合封装降低10-20℃,从而提高了芯片的稳定性和寿命,在尺寸和集成度方面,COP封装无需引线键合的键合空间,可以实现芯片与基板的高密度互连,封装尺寸更小,I/O间距可以缩小到几十微米甚至更小,满足了移动终端、可穿戴设备等对小型化、轻薄化的需求,COP封装的机械可靠性也优于引线键合,底部填充材料有效缓解了热循环和振动环境下的应力集中,减少了焊点疲劳失效的风险。

尽管COP封装技术优势明显,但其也存在一些挑战和局限性,首先是工艺复杂性和成本较高,凸块制作、对位贴片、底部填充等工序的精度要求极高,需要先进的设备和高良率的工艺控制,导致设备和材料成本增加,其次是凸块共晶焊接的质量控制难度大,焊接过程中容易出现虚焊、桥连、偏位等缺陷,对工艺参数(如温度曲线、压力、对位精度)要求严格,底部填充材料的流动性和固化收缩率也会影响封装可靠性,需要材料与工艺的协同优化,对于超大尺寸芯片(如300mm以上晶圆),COP封装的热应力和翘曲控制更为困难,需要采用先进的翘曲补偿技术和基板材料。

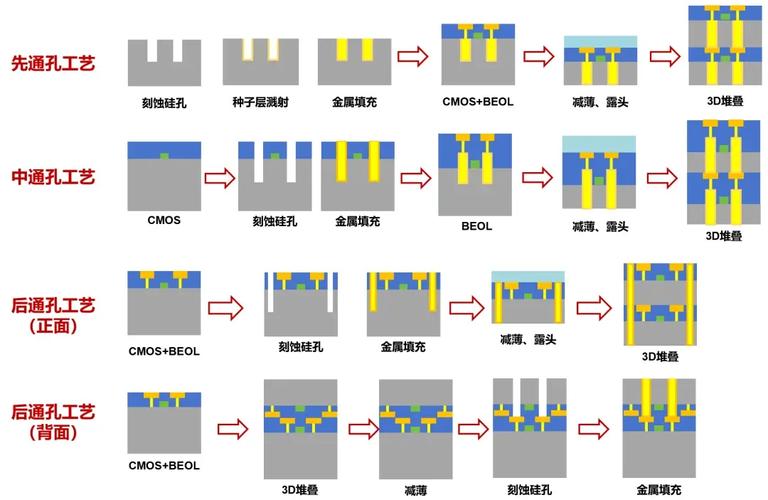

COP封装技术的应用领域广泛,涵盖了高性能计算、通信、消费电子、汽车电子等多个领域,在CPU和GPU中,COP封装通过缩短互连长度,提升了处理器的时钟频率和带宽,满足了数据中心和游戏对高性能的需求;在5G射频前端模块中,其优异的高频特性和散热性能保证了信号传输的稳定性和功率放大器的效率;在智能手机SoC中,小型化特性帮助实现了更薄的机身设计和更高的集成度;在汽车电子中,其高可靠性满足了严苛的环境要求(如-40℃~150℃的温度范围),随着异构集成(Heterogeneous Integration)技术的发展,COP封装已成为2.5D/3D封装(如硅通孔TSV、芯片堆叠)的核心互连技术,进一步推动了摩尔定律的延续。

为了更直观地对比COP封装与传统引线键合封装的差异,以下从几个关键维度进行总结:

| 对比维度 | COP封装技术(倒装芯片) | 传统引线键合封装 |

|---|---|---|

| 互连结构 | 芯片凸块与基板直接焊接 | 金丝/铜丝连接芯片焊盘与引脚 |

| 寄生电感 | 低(0.1-1nH) | 高(1-10nH) |

| 寄生电容 | 低(0.1-0.5pF) | 高(0.5-2pF) |

| 散热热阻 | 低(5-15℃/W) | 高(15-30℃/W) |

| I/O密度 | 高(间距可<50μm) | 低(间距通常>100μm) |

| 封装尺寸 | 小(无键合空间) | 较大(需键合区域) |

| 可靠性(热循环) | 优(底部填充缓解应力) | 一般(引线易疲劳) |

| 工艺复杂度 | 高(凸块制作、对位、底部填充) | 低(键合、塑封) |

| 成本 | 较高 | 较低 |

COP封装技术通过芯片凸块倒装互连的方式,显著提升了半导体器件的电气性能、散热效率和可靠性,满足了现代电子设备对高性能、小型化和高可靠性的需求,尽管其工艺复杂性和成本较高,但随着技术的不断成熟和规模化应用,COP封装已成为先进封装领域不可或缺的关键技术,并将在未来的异构集成和系统级封装(SiP)中发挥更加重要的作用。

相关问答FAQs

Q1:COP封装技术与传统引线键合封装相比,主要优势有哪些?

A1:COP封装技术的主要优势包括:①电气性能更优,寄生电感和电容极低,适合高频高速芯片;②散热性能更好,通过凸块直接传热,降低芯片结温;③尺寸更小,I/O密度更高,满足小型化需求;④机械可靠性更强,底部填充材料缓解热应力,减少焊点失效,这些优势使其在高性能计算、5G通信等领域更具竞争力。

Q2:COP封装技术的主要挑战是什么?如何解决?

A2:COP封装的主要挑战包括工艺复杂度高、成本大、凸块焊接质量控制难、大尺寸芯片翘曲控制难等,解决方法包括:①优化凸块制作工艺(如改进电镀参数)和贴片对位精度(采用高精度视觉对位系统);②开发低流动度、低收缩率的底部填充材料,并优化固化工艺;③采用高CTE匹配的基板材料和翘曲补偿技术(如应力缓冲层设计);④通过工艺窗口优化和自动化检测提高良率,降低长期成本。