DRAM地址复用技术是现代内存设计中的一项关键创新,主要用于解决高带宽需求与物理引脚限制之间的矛盾,在早期的内存设计中,地址线和数据线是独立的,随着内存容量的增加和访问速度的提升,地址线的数量急剧增加,这会导致芯片封装引脚数量过多,不仅增加成本,还会影响信号完整性和电路板布局的复杂性,地址复用技术通过时分复用的方式,将行地址和列地址共用同一组物理地址线,从而显著减少引脚数量,同时保持高性能数据传输。

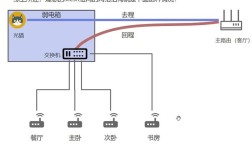

地址复用技术的基本原理是将地址传输分为两个阶段:首先传输行地址(Row Address, RAS),然后传输列地址(Column Address, CAS),通过控制信号(如RAS#和CAS#)的切换,内存控制器可以在同一组地址线上分时发送行地址和列地址,在一个时钟周期内,当RAS#信号有效时,地址线上传输的是行地址;随后当CAS#信号有效时,地址线切换为传输列地址,这种机制使得原本需要两组独立地址线的系统(如行地址10位+列地址10位=20位地址线)仅需10位物理地址线即可实现,从而节省50%的引脚资源。

地址复用技术的实现依赖于严格的时序控制,内存控制器和DRAM芯片之间需要精确同步,以确保地址和命令的正确传输,以DDR SDRAM(Double Data Rate SDRAM)为例,其地址复用过程与数据传输紧密耦合,在一个时钟周期内,地址线可能在上升沿传输行地址,在下降沿传输列地址,同时数据线在两个沿上各传输一次数据,实现双倍数据速率,这种设计不仅减少了引脚数量,还提高了数据吞吐量,地址复用技术还支持突发传输(Burst Transfer),即在确定起始地址后,DRAM自动按顺序传输连续的数据块,减少地址切换的开销,进一步提升效率。

地址复用技术的优势主要体现在以下几个方面:显著降低封装成本和复杂度,一个容量为1Gb的DDR4 DRAM,若采用非复用设计可能需要40位地址线,而复用后仅需10位地址线,加上控制线和数据线,总引脚数可控制在200脚以内,远低于非复用方案,提升系统可靠性,较少的引脚意味着更短的信号路径,降低了信号串扰和衰减的风险,特别是在高频操作下(如DDR4-3200的1600MHz频率),增强扩展性,随着内存容量和位宽的增加(如LPDDR5X的16位位宽),复用技术能灵活适应需求,避免引脚数量成为瓶颈。

地址复用技术也带来了一些挑战,时序设计变得更为复杂,需要精确控制RAS#、CAS#和时钟信号的相位关系,否则可能导致地址错误或数据丢失,在高速切换时,地址线的建立时间(Setup Time)和保持时间(Hold Time)必须严格遵守时序规范,否则可能引发信号竞争,地址复用对内存控制器的算法要求更高,需要优化地址预取(Prefetch)和调度策略,以减少行激活(Row Activate)和列选通(Column Strobe)之间的延迟,在连续访问不同行时,需插入行到列延迟(tRCD),而复用技术需更智能地管理这些延迟以避免性能损失。

以下表格对比了复用与非复用设计的关键差异:

| 参数 | 地址复用设计 | 非复用设计 |

|---|---|---|

| 地址线数量 | 减少约50% | 较多,与地址位宽成正比 |

| 封装引脚数 | 显著降低(如200脚以内) | 较高(可能超过300脚) |

| 信号完整性 | 更优(短路径、低串扰) | 较差(长路径、高串扰) |

| 时序复杂度 | 高(需精确控制RAS/CAS) | 低(地址独立传输) |

| 成本 | 低(封装和PCB成本) | 高 |

| 适用场景 | 高带宽、高容量内存 | 低速、小容量内存 |

在实际应用中,地址复用技术已从早期的SDRAM发展到DDR、DDR2、DDR3,再到最新的DDR5和LPDDR5X,DDR5进一步引入了8bank-group架构和12n预取,地址复用技术配合这些创新,实现了更高的数据速率(如DDR5-6400的3200MHz)和能效比,而在移动设备中,LPDDR系列通过地址复用技术实现了低引脚数(如LPDDR4X的24位地址/数据复用),适应紧凑的封装需求。

相关问答FAQs:

-

问:地址复用技术是否会降低内存访问速度?

答:不会,地址复用技术通过时分复用减少引脚数量,但配合突发传输和双倍数据速率等技术,反而提升了数据吞吐量,DDR SDRAM在地址复用的同时,在一个时钟周期内传输两次数据,有效带宽显著高于非复用设计,关键在于内存控制器的时序优化,确保地址切换与数据传输的高效协同。 -

问:为什么DDR5比DDR4的地址复用更复杂?

答:DDR5的地址复用设计更复杂,主要因为其引入了8bank-group架构和12n预取(DDR4为8n预取),地址线需要支持更多的bank-group选择和更宽的突发长度,DDR5采用双通道片上架构,地址复用需同时处理两个子通道的地址,增加了时序控制的难度,这些改进虽提升了性能,但对内存控制器的算法和信号完整性提出了更高要求。