人脸识别技术作为生物特征识别领域的重要分支,近年来在安防、金融、智能交通等场景得到广泛应用,其核心在于通过计算机算法对人脸图像进行特征提取与匹配,随着算法复杂度提升和实时性需求增长,传统CPU架构在处理大规模人脸识别任务时面临性能瓶颈,而FPGA(现场可编程门阵列)凭借其并行计算能力、低功耗和可重构特性,逐渐成为加速人脸识别系统的重要硬件平台,本文将围绕人脸识别技术与FPGA的结合,从技术原理、实现优势、关键设计及挑战等方面展开分析。

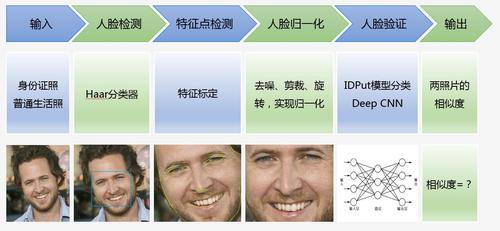

人脸识别技术的基本流程通常包括人脸检测、特征对齐、特征提取和匹配验证四个阶段,人脸检测旨在从图像中定位人脸区域,常用算法如Viola-Jones基于Haar特征和级联分类器,而深度学习方法如YOLO、SSD则能实现更精准的实时检测;特征对齐通过姿态估计和几何变换对齐人脸,消除角度、尺度差异;特征提取是核心环节,传统方法如PCA、LBP提取手工特征,而深度卷积神经网络(DCNN)如FaceNet、ArcFace通过学习高维嵌入向量显著提升识别精度;匹配阶段则通过计算特征向量间的余弦相似度或欧氏距离完成身份验证,这一流程涉及大量矩阵运算、卷积操作和向量内积,对计算资源提出高要求。

FPGA在人脸识别加速中的优势主要体现在硬件可重构性与并行性,与GPU相比,FPGA允许开发者根据算法特点定制硬件架构,通过流水线设计和并行处理单元实现数据吞吐量最大化,在卷积神经网络加速中,FPGA可将卷积操作分解为多个并行乘加单元,同时支持数据复用,减少内存访问开销,以典型的AlexNet网络为例,其包含96个3×3卷积核的第一层卷积层,在FPGA上可通过96个并行处理单元同时计算,每个单元负责一个卷积核的滑动窗口运算,显著提升处理速度,FPGA的低功耗特性使其适用于边缘计算场景,如智能摄像头、门禁系统等对能耗敏感的设备,而其可重构性则支持算法迭代升级,无需更换硬件即可优化性能。

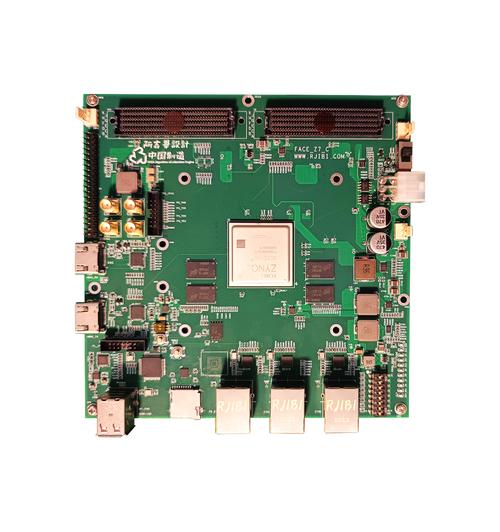

基于FPGA的人脸识别系统设计需关注多个关键技术点,首先是数据流优化,人脸图像数据需通过DMA(直接内存访问)控制器高效传输至FPGA内部,避免CPU干预造成的延迟;其次是算法硬件化,需将DCNN中的卷积、池化、激活函数等操作映射为硬件逻辑,例如用查找表(LUT)实现ReLU激活函数,用分布式RAM存储中间特征图;再者是资源平衡,FPGA的逻辑资源(LUT、FF)、存储资源(BRAM、URAM)和DSP资源需合理分配,例如DSP单元可用于加速卷积乘法运算,而BRAM则用于存储权重和特征图,以Zynq-7000系列SoC FPGA为例,其结合ARM处理器核心与可编程逻辑,可实现CPU与FPGA的异构计算:CPU负责控制流程和复杂逻辑,FPGA专注于图像预处理和特征提取,通过AXI总线实现高效数据交互。

在具体实现中,人脸检测与特征提取的硬件化存在差异,传统基于Haar特征的人脸检测器因算法简单,可在FPGA上通过积分图计算和并行分类器实现实时处理,而深度学习检测器如YOLO则需更复杂的硬件支持,如多级流水线设计处理不同尺度的特征图,特征提取环节,FaceNet网络的Triplet Loss计算涉及大量向量内积,FPGA可通过定制化的向量乘加单元实现并行计算,同时量化技术(如将32位浮点数转换为16位定点数)可减少资源占用,提升处理速度,某研究团队在Xilinx VCU118 FPGA上实现了ArcFace算法,通过8位量化将资源占用降低50%,同时保持99.2%的识别准确率,处理速度达到300fps(1080p分辨率)。

尽管FPGA在人脸识别中展现出优势,但仍面临挑战,首先是开发复杂度高,传统硬件描述语言(VHDL/Verilog)开发周期长,需结合高层次综合(HLS)工具如Vivado HLS缩短设计时间;其次是算法兼容性,FPGA对动态数据结构的支持较弱,需将神经网络中的动态计算(如变长卷积)转换为静态硬件逻辑;再是成本问题,高端FPGA芯片价格较高,需在性能与成本间找到平衡,随着7nm以下工艺制程的推进,FPGA的功耗和散热问题也需关注,通过时钟门控、电源管理技术可进一步优化能耗。

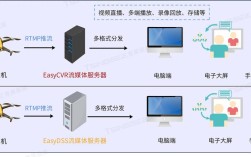

FPGA与边缘AI的结合将推动人脸识别向更高效、更低功耗方向发展,5G网络的普及将使FPGA加速的人脸识别终端在分布式系统中发挥更大作用,如智能城市的多摄像头协同分析;而Chiplet(芯粒)技术的成熟可能降低FPGA成本,促进其在消费级电子中的应用,与存算一体化架构的结合有望解决“内存墙”问题,进一步提升数据传输效率。

相关问答FAQs

-

Q:FPGA与GPU在人脸识别加速中各有什么优劣势?

A:FPGA的优势在于硬件可重构性,能针对特定算法优化并行架构,功耗更低,适合边缘计算;劣势是开发难度大,成本较高,GPU则凭借成熟的CUDA生态和大规模并行核心,适合通用深度学习任务,但功耗较高,灵活性不足,对于定制化强、实时性要求高的人脸识别场景(如嵌入式设备),FPGA更具优势;而对于大规模云端识别任务,GPU更高效。 (图片来源网络,侵删)

(图片来源网络,侵删) -

Q:如何解决FPGA开发中算法硬件化的效率问题?

A:可通过以下方法提升效率:采用高层次综合(HLS)工具,用C/C++描述算法逻辑,自动生成硬件代码;利用IP核(如Intel的OpenVINO Toolkit或Xilinx的DNN)复用成熟模块;结合量化技术降低数据精度,减少资源占用;采用流水线设计优化数据流,避免计算瓶颈,针对特定算法(如CNN)的专用架构(如脉动阵列)可显著提升计算效率。