基带芯片作为移动通信设备的核心部件,承担着数字信号处理与射频通信的关键功能,而SOC(System on Chip,片上系统)技术的融合则推动其向更高集成度、更低功耗和更强性能的方向发展,从1G时代的独立芯片到如今5G SoC平台的异构集成,基带芯片的技术演进始终与通信标准迭代和半导体工艺进步深度绑定,其背后是SOC架构设计、多模融合、功耗管理等核心技术的持续突破。

基带芯片的本质是实现通信协议栈的硬件化,在早期移动通信中,基带处理单元与射频模块、应用处理器分离设计,导致设备体积庞大、功耗高昂,2G时代的基带芯片仅支持单一制式(如GSM或CDMA),需外接DSP(数字信号处理器)进行基带运算,而射频前端则依赖多个独立器件协同工作,这种分立式架构不仅增加了系统复杂性,也限制了通信性能的提升,随着3G时代的到来,多模需求(如WCDMA与TD-SCDMA兼容)成为市场刚需,基带芯片开始集成多协议处理单元,但仍难以满足智能手机对小型化、低功耗的要求,直到4G LTE时期,SOC技术的大规模应用才真正改变了基带芯片的设计范式——将基带处理器、CPU、GPU、DSP、射频收发器等单元集成到单一芯片中,并通过高速总线(如NoC,Network on Chip)实现数据交互,大幅降低了系统延迟和功耗。

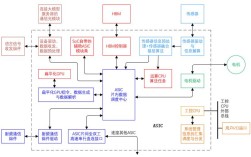

SOC技术在基带芯片中的核心价值体现在集成度的飞跃与系统效率的优化,从架构层面看,现代基带SoC通常采用异构多核设计,针对不同任务特性定制处理单元:ARM Cortex-A系列CPU负责运行通信协议栈和应用层逻辑,专用DSP处理信道编码/解码等数学密集型任务,GPU则加速图形与AI计算;基带SoC还集成基带带DSP(Baseband DSP)、射频收发器(RF Transceiver)、电源管理单元(PMU)等模块,甚至集成NPU(神经网络处理器)以支持5G Massive MIMO的波束赋形算法,这种异构集成不仅减少了芯片间互连的延迟和功耗,还通过共享缓存和内存池提升了数据吞吐效率,以5G基带SoC为例,其集成度可达数十亿晶体管,支持Sub-6GHz与毫米波多频段、SA/NSA组网模式,同时处理下行4.9Gbps与上行上行1.2Gbps的数据速率,而功耗却较4G时代降低约30%,这得益于SOC技术带来的工艺升级(如7nm/5nm EUV制程)和架构创新(如动态电压频率调节DVFS)。

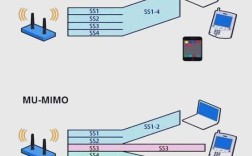

多模多频融合是基带SoC的另一关键技术挑战,全球通信标准长期呈现碎片化特征(2G/3G/4G/5G共存,不同国家/地区频段差异显著),基带SoC需通过软件定义无线电(SDR)技术实现协议可重构,具体而言,基带SoC中的基带带DSP采用可编程架构,通过固件升级支持不同制式的调制解调算法,而射频前端则集成多频段功率放大器(PA)、低噪声放大器(LNA)和开关矩阵,通过软件配置切换工作频段,高通骁龙X65基带SoC支持全球超过40个5G频段,涵盖Sub-6GHz的n1/n3/n5/n7/n8等频段及毫米波的n257/n258/n260等频段,这种灵活性依赖SOC技术对射频与基带单元的高效协同——通过片上ADC/DAC实现射频信号的数字化处理,减少外部模拟器件的数量,同时通过实时操作系统(RTOS)动态分配计算资源,确保多模并发时的实时性。

功耗管理是基带SoC设计的核心难点,5G通信的高速率与低延迟特性对芯片功耗提出更高要求,毫米波频段的射频单元功耗可达数瓦,而智能手机电池容量有限,基带SoC通过多层次功耗管理技术应对这一挑战:在架构层面,采用大小核设计(如Cortex-A78大核+Cortex-A55小核),根据业务负载动态激活核心;在电路层面,集成自主电源管理单元,对各模块电压/电流进行独立调节;在系统层面,通过AI算法预测网络状态,提前调整功耗策略(如从4G待机切换至5G深度休眠模式),以联发科天玑9000 5G SoC为例,其集成APU 590 AI处理器,可实时分析用户行为,智能调度基带与GPU资源,在5G峰值下载场景下功耗较传统方案降低20%。

基带SoC技术将向6G、AI融合与异构集成进一步演进,6G通信对太赫兹频段、超大规模MIMO(如128T128R)的支持,要求基带SoC集成更高性能的AI加速器,以实时处理信道估计与波束训练数据;Chiplet(芯粒)技术可能成为主流,通过先进封装(如2.5D/3D IC)将不同工艺节点(如基带用5nm,射频用22nm)的芯粒集成,在提升性能的同时降低成本,基带SoC与边缘计算、云计算的协同也将成为趋势,通过分布式算力调度实现通信与计算的一体化。

相关问答FAQs

Q1:基带芯片与SOC技术的区别是什么?

A:基带芯片是专门处理通信信号(如调制解调、编解码)的半导体器件,而SOC是一种集成技术,将多个功能模块(如CPU、GPU、基带、射频等)集成到单一芯片上,基带芯片可以是独立器件,也可以是SOC的一个组成部分;现代基带芯片普遍采用SOC技术,以实现更高集成度和系统效率。

Q2:5G基带SoC为何需要AI加速器?

A:5G通信中的Massive MIMO、波束赋形、动态频谱共享等技术需要实时处理海量信道数据,传统DSP难以满足低延迟需求,AI加速器(如NPU)通过专用神经网络计算单元,可高效完成信道预测、干扰消除等任务,同时支持AI驱动的功耗优化,例如根据网络环境智能调整发射功率,从而提升通信效率并降低能耗。